USB2.0主机控制器IP核的设计

出处:davywan 发布于:2011-08-30 14:04:26

摘要 :为了摆脱对USB2.0 主机控制器ASIC 芯片的依赖,提高产品集成度,本文设计了针对全速和高速USB 海量存储设备的USB2.0 主机控制器IP 核。首先介绍USB2.0 主机控制器IP核中主要涉及的USB2.0 通信协议以及与物理层芯片接口的ULPI 接口规范协议,并依据协议规范,利用VHDL 硬件描述语言完成USB2.0 主机控制器IP 核的ULPI 接口模块以及USB2.0通信协议模块的设计。使用Xilinx 公司的ISE Simulator 工具进行波形仿真,并在XilinxXUPV2 开发板上进行验证,仿真结果及FPGA片上实验表明本文设计的USB2.0 主机控制器能够完成对USB 海量存储设备的有效管理。

0 引言

在USB 协议标准发展的过程中,USB2.0 接口凭借其连接简单、稳定、速度快以及即插即用等优点,广泛应用于计算机、通信和消费类电子产品中。然而目前大部分USB 主机端控制器都是使用国外公司研制的专用ASIC 芯片,USB2.0 主机控制器IP 核的设计可以摆脱对这些芯片的依赖,使得应用灵活方便。本文完成了针对全速和高速海量存储设备USB2.0主机控制器IP 核中与物理层芯片接口的ULPI[2]模块以及USB2.0 协议模块的设计和实现。

ULPI 模块介于USB2.0 主机控制器的协议模块和物理层芯片之间,完成对插入USB 设备的状态检测,判别是何种设备(全速还是高速),然后将设备置于相应的状态再进行USB 的各种传输事务。每一个USB 的传输都是由事务组成的。而每一个事务都是由USB 传输的基本单位包(packet)来组成的,USB 的包主要是由令牌包、数据包、握手包和特殊包这四种类型组成的。令牌包和数据包又包含不同的类型[4],握手包仅由一个PID 域组成用以传输联络信号来反映目前数据处理的状态。USB 协议包含了四种数据传输类型,分别为控制传输,批量传输,中断传输和同步传输,其中控制传输是所有设备必须要支持的传输方式,对时间没有严格限制的大量的数据传输要用到批量传输;同步传输也被称为实时传输。

1 系统设计

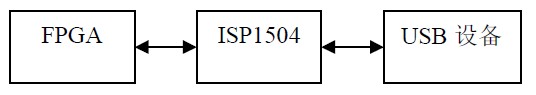

图1 整体系统图

图 1 中FPGA型号为Xilinx Virtex-II proxc2vp30,标识为ISP1504 的子板通过FPGA扩展口接入到FPGA 开发板,子板以物理层芯片ISP1504 为并配以简单外围电路构成,上面带有USB 接口用来插入USB 设备。ISP1504 用来完成数据的串行化和解串,以及NRZI编码和比特位填充等功能。FPGA 中内嵌microblaze 软核处理器,USB 主机控制器IP 核作为用户IP 核挂接到处理器的PLB 总线上,再加入USB 驱动,便可以实现microblaze 处理器对全速和高速USB 海量存储设备的管理。本文主要介绍USB 主机控制器IP 核设计中的两个重要模块--与物理层接口的ULPI 模块以及USB2.0 协议层模块的设计实现。

2 ULPI 接口模块的设计及实现

ULPI(UTMI+低引脚数)接口规范是应用于高速通用串行总线(USB)和便携式USB(USBOTG)收发器芯片的行业规范。ULPI 模块提供USB 主机控制器与UTM 正常通信的物理层通道,是主机控制器实现正常通信的重要接口之一。该模块依据ULPI规范实现了总线事件检测的功能,完成了上电,正常操作,挂起和复位状态之间的转换等。

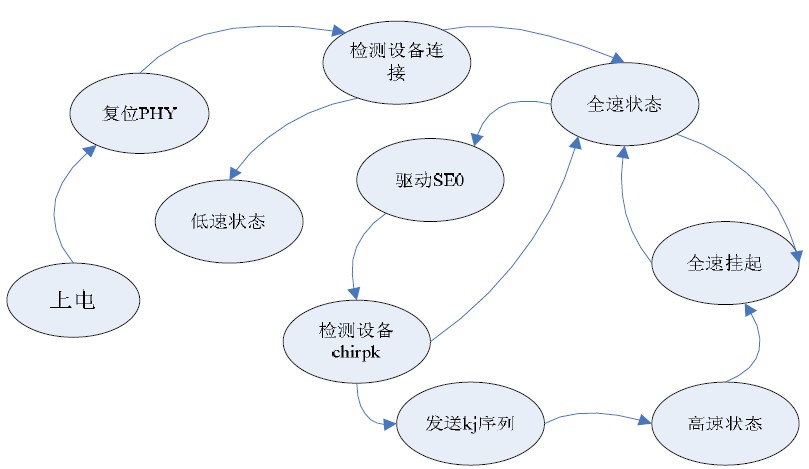

此模块采用状态机来实现,主要通过对 ISP1504 的功能控制寄存器写入一定的数据,使得物理层芯片的收发器进入相应的状态(全速、高速以及高速挂起),对状态机中时间控制采用计数器实现,主机端发送kj 序列对首先通过写ISP1504 的功能控制寄存器使之进入高速chirp 检测状态,然后在数据线上发送全0 和全1 来完成的。本设计USB2.0 主机控制主要针对全速和高速海量存储设备设备,全速和高速的状态转移图如图2 所示:

图 2 ULPI 模块状态转移图

芯片上电之后,通过写ISP1504 的功能控制寄存器的reset 位来复位芯片,之后通过差分数据线的状态来检测是否有设备插入,并根据状态判断是低速设备还是全速设备(D-为高电平,即连接的设备为低速设备。若D+为高电平,即连接的设备为全速设备。)需特别说明的是,主机端对高速设备的检测并不是一下完成的,是首先置为全速设备,然后主机端通过设置控制功能寄存器驱动出SE0 信号,如果收到设备发回的chirp k信号,主机端就会发送线性调频的kj 序列对,每个k 或者j 持续时间在40-60us,如果设备是高速设备,在检测到主机发过来的3 个kj 序列对之后设备的控制器会使其自身进入高速模式,即高速收发正常的操作状态。如果没有收到设备返回的chirp k 信号则认为是全速设备回到全速状态下进行传输。当总线上没有数据传输(空闲状态)超过3ms,则会进入FS 挂起状态,当收到主机端发送的resume信号时恢复到FS状态,同理如果在高速状态下空闲超过3ms,会先进入FS挂起状态。

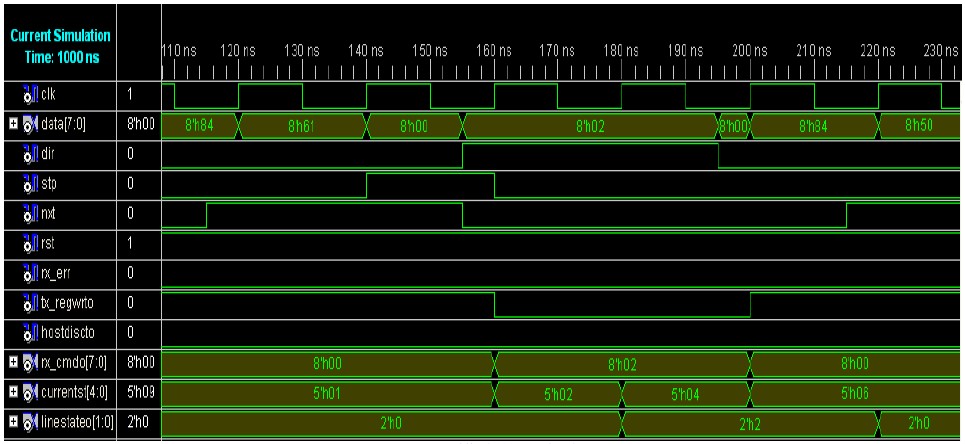

用 VHDL 硬件描述语言完全按照上述状态机转移完成此模块,在Xilinx ISE 开发环境下使用ISE simulator 仿真工具进行仿真,仿真波形如图3 所示:

图3 ULPI模块的仿真波形

由于状态转移对时间的限制,故只截取了部分状态作分析。由图所示,currentst[4:0]反映的是状态机的状态,linestate[1:0]表示线上状态(直接反映D+ D-状态),在状态1 通过向ISP1504 的84H 地址(控制功能寄存器的地址)写入61H(置位rst 位)复位物理层芯片。

在状态1 写完寄存器后置位stp,转到状态2 检测设备连接状态。在状态2,当检测到linestate变为10(D+为高),所以先识别为全速设备,转到全速状态4。在下一个时钟周期进入状态6 驱动se0 对设备进行复位,然后按照状态转移图进入高速操作阶段。

3 USB2.0 协议模块的设计和实现

在 ULPI模块完成了设备的状态监测和转移之后,等进入正常的全速或者是高速模式,就可以按照USB2.0 协议完成数据的传输,USB2.0 协议实现模块是主机控制器实现的模块,完成USB 数据的读写和传输方式的控制。根据协议层的功能主要把协议层分成三个子模块来实现,分别是封包模块(PA)、拆包模块(PD)以及控制传输的协议引擎模块( PE )。

3.1 PA PD 模块的设计实现

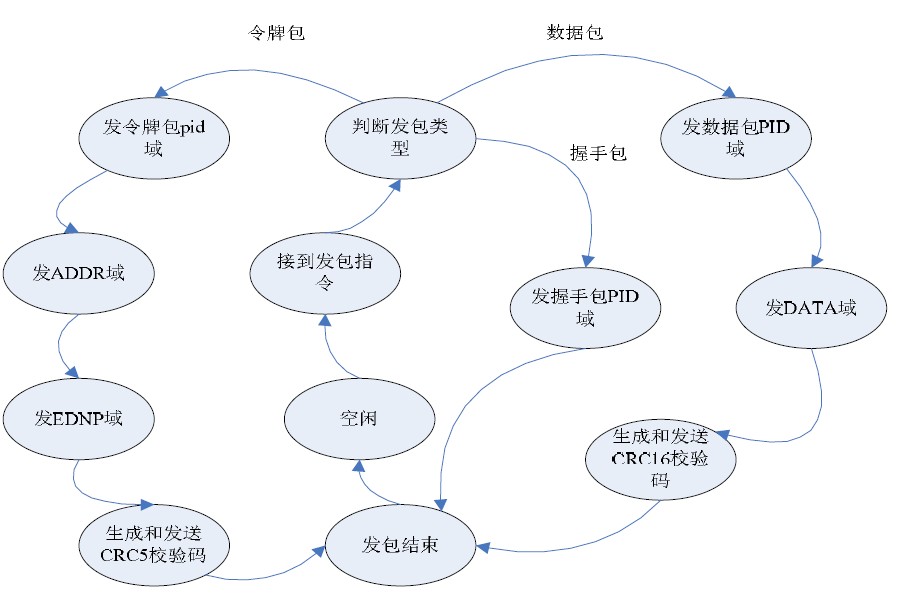

封包模块(PA)需要对令牌包、数据包和握手包三种包按照其对应格式分别进行封装并发送到ULPI 模块。开始空闲状态,接到发包指令后,判断发包类型然后进入相应的状态。例如令牌包需将其PID 域、ADDR 域、ENDP 域以及CRC5 校验域按照顺序封装完成后发送。

状态转移图如下所示:

图4 PA模块状态转移图

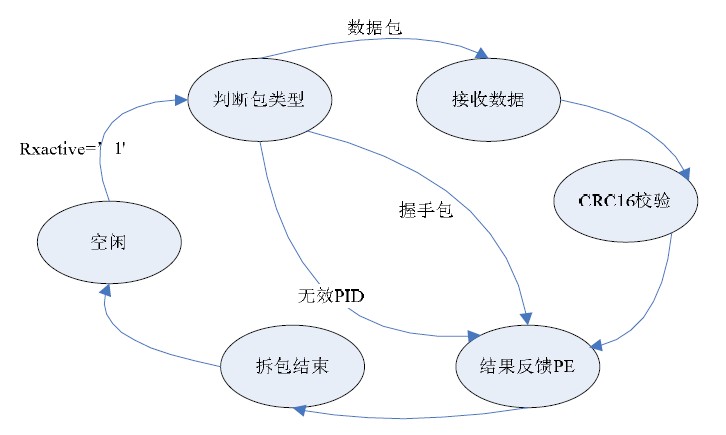

拆包模块(PD)刚好是封包模块的逆过程,该模块是把从ULPI 模块接收到的数据包和握手包进行拆包。对数据包拆包首先就是要判断PID 域以确定数据包的类型,并且还需对数据进行CRC 校验然后根据该数据包的功能将数据域内容送给要保存数据的模块,图5 是拆包模块的状态转移图:

图 5 PD 模块状态转移图

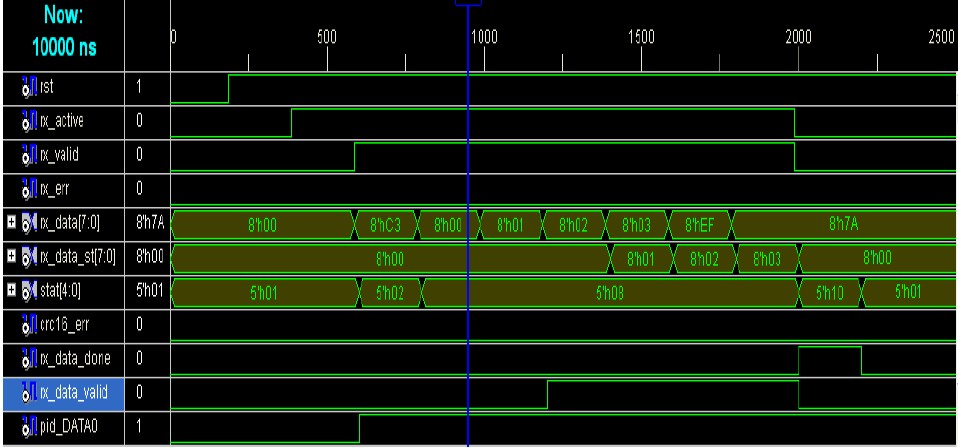

仿真结果如图6 所示:

图 6 拆包的仿真波形

在图6 中,完成一个包含三个数据域的拆包过程。信号rx_valid 和rx_active 同时有效时rx_data[7:0]代表从ULPI 模块接收到的数据,首先根据接收PID 域值为C3,判断出该数据包的类型为DATA0,pid_data0 信号为高。Rx_data_st 保存拆包完成后的数据域,数据是在rx_data_valid 信号为高电平期间存入rx_data_st 寄存器的,所以接收数据为0x00、0x01、0x02、0x03。对接收的CRC 部分进行了验证,由于0xef、0x7a 是此包数据域正确的CRC 生成码,所以传输无误情况下crc16_err 一直为0。

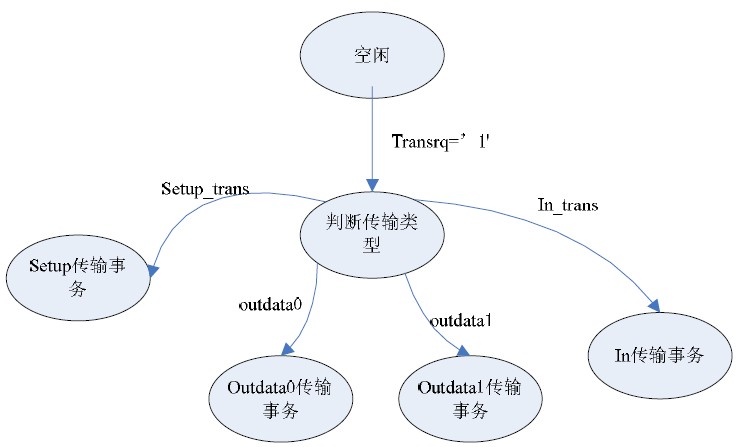

3.2 PE 模块的设计实现

协议引擎(PE)模块主要负责协调PA 和PD 模块实现USB 传输方式,本设计主要实现两种传输方式即控制传输方式和批量传输方式。该模块设计的主状态转移图如图7 所示,状态机在空闲状态收到请求传输有效信号transreq后,就会对请求类型transtype进行判断。不同的transtype 值代表着不同的传输事务要求。按照不同的要求,主状态机就会转到相应的传输事务状态中进行处理。

图 7 PE 模块主状态转移图

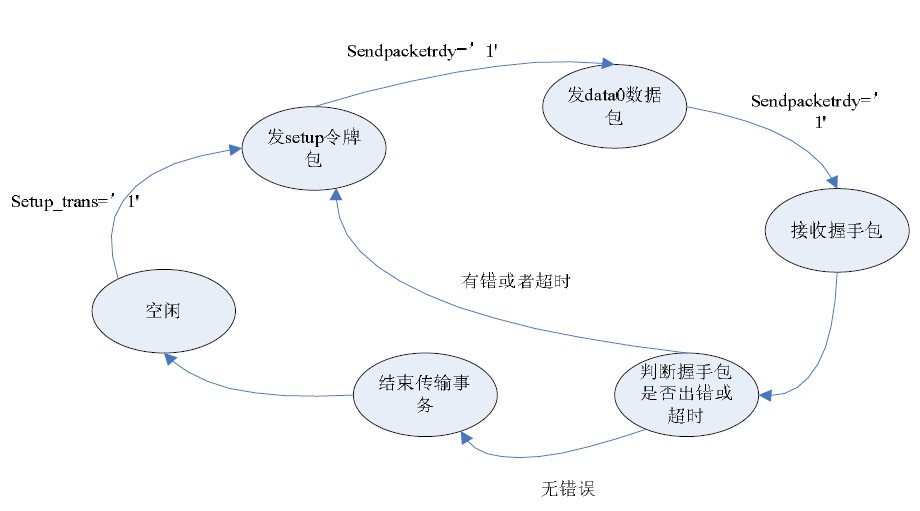

每个传输事务由不同的状态转移过程来实现,以其中的setup 传输事务为例。首先,状态机向PA 模块发送发包使能标志,同时将表示setup 令牌包的值"1101"送给PA 模块。PA模块接到发setup 包指令,就会按照要求完成封包发送的工作,反馈给PE 模块一个发包结束的信号sendpacketen。setup状态机接收到发包结束信号sendpacketen为'1'后,就会转到下一个状态发data0 数据包。在此状态下如果收到发包结束有效信号,也会转到下一状态接收握手包。在这个状态中,主要是和PD 模块进行通信。PD 模块通过对接收的握手包进行拆包,来分析包的PID 域是否出错。如果没有错就会反馈给PE 模块包的类型,出错就通过信号来通知PE 模块。状态机本状态除了要判断接收包是否出错,还要判断接收包是否超时。各个事务分别完成之后,至此协议层完成。

图 8 Setup 事务状态转移图

4 结论

本文完成了 USB2.0 主机控制器中ULPI 模块与USB2.0 协议层模块设计,此USB2.0 主机控制器 IP 核主要针对全速和高速海量存储设备。设计采用VHDL 语言进行RTL 级描述,使用Xilinx 公司的ISE simulator 工具进行波形仿真,仿真结果验证了设计的正确性,并且在Xilinx XUPV2 FPGA 开发板[8]和带有USB接口并以物理层芯片ISP1504为的子板上进行了验证。本文设计的USB2.0 主机控制器可作为独立的IP 核移植到其他数字系统中,摆脱对USB2.0 主机控制器ASIC 的依赖,提高产品集成度。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- EPS Global - 谁需要嵌入式安全?2024/4/22 15:39:31

- 什么是嵌入式SoC2024/4/3 16:20:28

- EasyARM-i.MX283(7)A 默认供电方案2024/3/28 17:39:53

- EasyARM-i.MX283(7)A 的快速入门2024/3/27 17:29:30

- 非线性数字滤波器:用例和示例代码2024/3/14 16:34:20