基于FPGA的多功能数字钟设计

出处:baillso 发布于:2012-12-17 11:57:20

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是一种可编程使用的信号处理器件。通过改变配置信息,用户可对其功能进行定义,以满足设计需求。通过开发,FPGA能够实现任何数字器件的功能。与传统数字电路相比,FPGA具有可编程、高集成度、高可靠性和高速等优点。

1 数字钟总体设计

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现的功能如下:

1)计时功能:进行正常的时、分、秒计时,并由6只8段数码管分别显示时、分、秒时间。

2)校时功能:当时校时按键按下时,计时器时位迅速增加,并按24小时循环;当分校时按键按下时,计时器分位迅速增加,并按60分循环。

3)整点报时功能:当计时到达59分53秒时开始报时,在59分53秒、55秒、57秒蜂鸣声频率为512 Hz;到达59分59秒为一声报时,蜂鸣声频率为1 kHz.

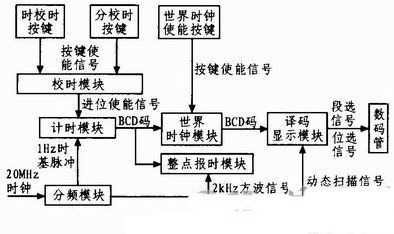

4)世界时钟功能:默认当前显示时间为北京时间(GMT+8),当按下世界时按键时,显示时间将转换为格林威治标准时(GMT)。数字钟电路的模块框图,如图1所示。

2 功能模块的工作原理及设计实现

系统主要由6大模块组成,即分频模块、计时模块、校时模块、译码显示模块、整点报时模块和世界时钟模块。

2.1 分频模块的工作原理及设计实现

本设计选用的FPGA开发板板载20 MHz有源晶振,为了得到占空比50%的1 Hz时基脉冲及2 kHz方波信号(用于驱动译码显示模块以及为整点报时模块提供不同频率的信号以产生不同音调的声音),需要对板载时钟信号进行分频。分频模块采用VHDL语言实现,对20 MHz时钟信号分别进行两千万和一万分频。具体实现代码如下:

2.2 计时模块和校时模块的工作原理及设计实现

计时模块由60进制秒计数器、60进制分计数器和24进制时计数器级联构成,采用同步时序电路实现。当计数器处于正常计数状态时,3个计数器的时钟信号均为1Hz时基脉冲,秒计数器对1 Hz的时基脉冲进行计数,其进位输出信号cos_in作为分计数器的使能信号,而分计数器的进位输出信号com_in又作为时计数器的使能信号。在计时模块的基础上,数字钟通过增加两个按键分别实现对小时和分钟的调整。这两个按键能够产生时计数器和分计数器的另一路使能信号,即按下时校时按键时,时计数器使能信号持续有效,由于采用同步时序电路,时计数器能够持续增加,达到调整时间的目的。按下分校时按键时原理相同。此外,校时模块还对校时按键进行防抖动处理,提高系统的可靠性和抗干扰能力。

2.3 译码显示模块的工作原理及设计实现

译码显示模块采用原理图方式实现。本设计选用的FPGA开发板设有6位8段共阳极数码管,并采用动态显示方式。计时模块输出秒低位、秒高位、分低位、分高位、时低位、时高位共6x4路信号,经由74151数据选择器选择1×4路信号,该信号通过74248显示译码器得到驱动8段数码管的1组段选信号(段码)。同时,2 kHz方波信号经由74160分频得到3路信号,驱动74151及74138 3:8译码器产生位选信号(位码)。

2.4 整点报时模块的工作原理及设计实现

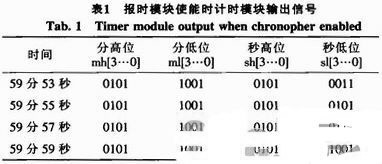

整点报时模块根据秒计数器、分计数器输出的数值决定是否报时,当时间为59分53秒、55秒、57秒时,报时频率为512Hz;当时间为59分59秒时,报时频率为1 kHz.不同频率的信号通过蜂鸣器产生不同音调的蜂鸣声。报时模块使能时,计时模块输出信号如表1所示。

2.5 世界时钟模块的工作原理及设计实现

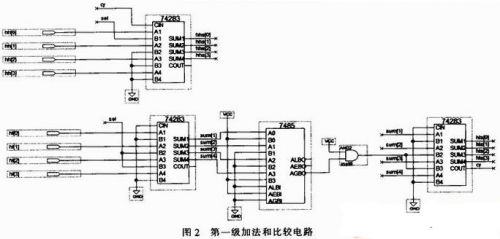

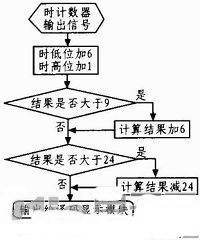

本设计中加入了世界时钟模块,能够将北京时间快速转换为格林威治标准时。北京位于东八区,格林威治位于本初子午线附近,北京时间比格林威治标准时快8小时,要完成时间转换,需要将北京时间减去8小时,在24进制中相当于加16小时。基于此设计加法和比较电路。在时计数器输出信号的基础上,利用74283四位全加器将时低位加6(01102),时高位加1(0001 2)。由于74283四位全加器为16进制,而时较器判断计算结果是否大于9,若结果大于9,则需要在此基础上继续加6,将结果修正为十进制,过程中产生的进位信号作为时高位的CIN信号;若结果小于9,则可直接输出。级加法和比较电路如图2所示。完成时低位加6,时高位加1的变换后,需要判断变换后的时间是否大于24.若大于24,则需要减24;若小于24,则可直接输出。世界时间转换流程图如图3所示。

3 结束语

在QuartusⅡ开发环境中完成上述各模块的原理图设计和程序编写,并对设计好的电路进行编译、仿真,得到的仿真波形符合设计要求。根据所采用的硬件平台,在顶层电路中进行管脚分配、再编译。然后将编译好的目标文件到FPGA开发板中进行验证和调试。测试结果,数码管能够正确显示计时时间,能够通过按键调整时间,整点报时和世界时钟均能够正常工作,实验结果符合设计要求。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 什么是嵌入式SoC2024/4/3 16:20:28

- EasyARM-i.MX283(7)A 默认供电方案2024/3/28 17:39:53

- EasyARM-i.MX283(7)A 的快速入门2024/3/27 17:29:30

- 非线性数字滤波器:用例和示例代码2024/3/14 16:34:20

- 嵌入式微控制器的自动代码生成2024/2/26 16:51:13