用双MicroBlaze监控汽车应用

出处:电子系统设计 发布于:2012-02-01 09:28:26

基于软核处理器的多处理器片上系统(MPSoC)设计正日益风靡于嵌入式系统设计领域。为了向多个处理器提供一致的数据,存储区架构和管理已成为设计工作中非常重要的组成部分。在原型汽车应用中,我们准备构建一个双MicroBlaze系统,用于在两个MicroBlaze上支持赛灵思(Xilinx)公司嵌入式处理器内核Xilkernel.

在开发自主汽车原型转向平台前,我们根据Xilinx技术规范、参考设计和双处理器设计套件,研究出一套通用的设计工作流和工艺。该设计结合了多种功能,比如:防碰撞、行车道检测和自动停放。Xilkernel设计提供了诸如Posix线程这样的库函数,可重复利用基于QNX的防碰撞应用以及对其进行分割。

紧密连接

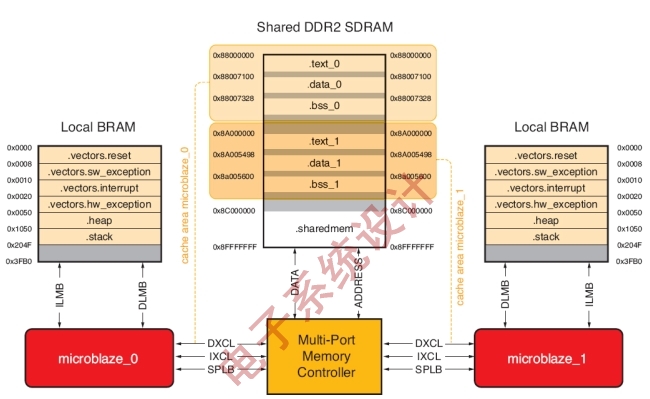

我们构建了一个紧密连接的处理器系统,内含两个配置完全相同的MicroBlaze处理器,在Harvard架构中,每个处理器都与一个16KB的局部块RAM(BRAM)相连(图1)。另外,这两个处理器还与一个128MB的DDR存储器模块相连,用于存储代码和数据交换。Xilinx平台工作室(XPS)Mutex内核负责对两个MicroBlaze共享的存储器访问进行同步。两个处理器还能通过一对快速单工链路(FSL)直接通信,FSL支持主/从和流水线处理器设计概念。采用FSL实现这两个MicroBlaze的互联,而不采用XPS Mailbox实现,可以提高性能,并降低资源耗用。

图1:面向XtremeDSP开发平台的双MicroBlaze Xilkernel配置。

两个定时器外设负责为Xilkernel的调度实现提供中断源。开发阶段的步,我们通过UART接口将激光扫描仪连接到系统,为防碰撞系统提供目标检测。为以中断控制器而非直接连接的时钟中断部署Xilkernel,我们在板支持包(BSP)设置中调整了与Xilkernel相关的参数sysintc_spec.

我们把两个MicroBlaze连接到MicroBlaze调试模块进行调试,并通过microblaze_1的JTAG UART输出ST.DIO.我们分析了系统的两种实现方案,一种用XtremeDSP开发平台搭配Spartan-3A DSP 1800A FPGA,另一种用ML605评估板搭配Virtex-6 XC6VLX240T FPGA.

存储器和高速缓存架构

多端口存储器控制器(MPMC)通过Xilinx缓存链路(XCL)将Microblaze与外部DDR2存储器相连,并分配直接存储访问。由于采用统一的存储器架构,每个处理器具有相同的存储延迟和访问方式。我们为每个MicroBlaze配置了8KB指令和8KB数据缓存,均连接到单一MPMC PIM.这种布线方式可以让我们将多8个MicroBlaze关联到一个MPMC.

单一MPMC地址总线连接和数据总线连接,会导致MPMC与外部存储器之间出现数据流和取指瓶颈。但内部的时间片轮转仲裁,能够保证所有请求都能顺序访问存储器。另外,MicroBlaze还能通过处理器局部总线(PLB)保持与MPMC的连接,以提供对无缓存共享存储区的访问。

在多处理器环境中,确保数据高速缓存的一致性非常重要。因此,我们将外部存储的地址范围分为三段(图2)。每个MicroBlaze占有自己的地址空间,而只有数据存储在其特定的区域,XCL才会缓存数据。第三个地址空间提供一个独立段,可通过PLB访问,而用于交换未缓存的共享数据。通过在链接脚本中预定义变量,软件工程师可以得到一个指向该段基址的指针。我们用写通策略配置高速缓存,因为如果采用回写策略,处理多个写访问会导致更多延迟。

图2:DMX系统的内存印象图

连接器脚本的配置

连接器脚本的作用是,根据硬件设计信息,正确的板支持包和软件应用本身,来定义处理器系统的存储分段。XPS工具负责为每个MicroBlaze的复位、中断和异常向量分配固定段,这些向量将存储在处理器的BRAM中。常用的方法是把。heap和。stack段也存储在局部BRAM中,以便在执行线程的时候快速访问局部变量。

考虑到实时操作系统(RTOS)具有众多库函数,.text和。data段对BRAM显得过大,因此,我们将这些函数存放在外部存储器中。在多处理器系统中,如果多个处理器需要对相同存储区域寻址,这样做会导致问题复杂化。因此,开发人员必须手动调整存储分段。如前文所述,两个处理器只缓存自己专用的存储区,并共享对代码段和数据段之外定义区域的访问。通过PLB请求XPS Mutex,可对该共享存储区域进行同步访问,从而实现在两个MicroBlaze之间交换数据。为了在主/从或者流水线处理器系统中实现直接通信和同步,我们采用了FSL.这样可以避免在访问共享存储器时,因多次存储器总线分配而导致更高的访问延迟。

我们首先使用SDK链接脚本生成程序创建链接脚本。该脚本为文本文件,由三段组成,定义了堆和栈的大小、存储区以及每个段的地址。下段代码描述了双MicroBlaze Xilkernel系统Microblaze_0的链接脚本。我们调整了代码段和数据段存储区的大小,并增加了一个用于共享存储区的新段。我们也相应调整了microblaze_1的链接脚本,将代码段和数据段的起始存储区地址设定为0x8A000000,并为共享存储器分配了一个相等的段。

/*定义microblaze_0的堆和栈大小*/

_STACK_SIZE = DEFINED(_STACK_SIZE) ? _STACK_SIZE :

0x1000;

_HEAP_SIZE = DEFINED(_HEAP_SIZE) ? _HEAP_SIZE :

0x1000;

/*定义系统中用于microblaze_0的存储器*/

MEMORY

{

ilmb_cntlr_dlmb_cntlr :

ORIGIN = 0x00000050, LENGTH = 0x00003FB0

/*重新设定用于代码段和数据段的存储器大小*/

DDR2_SDRAM_MPMC_BASEADDR :

ORIGIN = 0x88000000, LENGTH = 0x02000000

/*为共享存储器新增一个分段*/

DDR2_SDRAM_SHARED_BASEADDR :

ORIGIN = 0x8C000000, LENGTH = 0x04000000

}

[…]

/*定义各段和它们在存储器中映射的位置*/

SECTIONS

{

[…]

sharedmem : {

__sharedmem_start = .;

*(sharedmem)

__sharedmem_end = .;

} > DDR2_SDRAM_SHARED_BASEADDR

[…]

}

MPSOC的和调试选项

SDK环境为、运行和调试多处理器系统的软件提供了两种方法。一方面,基于Eclipse的工具能够为软件工程提供和ST.DIO状态的配置;另一方面,可以使用Xilinx微处理器调试(XMD)控制台来处理这些任务。

另外,SDK还可以使用位流和。bmm文件重配置FPGA.根据链接脚本中定义的段,FPGA编程对话框(Program FPGA Dialog)可以随意将整个软件段直接传输到与特定处理器相关联的BRAM中。如上所述,由于。elf文件会因使用Xilkernel库函数的应用而增大,因此,在多处理器系统中,我们一般会将这些段存放在外部存储器中。在这种情况下,可以选择FPGA编程对话框软件配置设置中的bootloop,来提供后续的软件。

SDK环境

SDK在工程浏览器(Project Explorer)窗口中,提供了包括软件工程选择的运行与调试(Run & Debug)配置,以及在Run菜单中打开"Run configurations…".系统中每个处理器都有相关联的"Run & Debug"配置。在个例子中,选择配置对话框主标签中的工程。elf文件。在"Device Initialization"标签中将"Reset Processor Only"选为复位方式,以避免在复位时将整个系统重置。

另外,通过配置ST.DIO Connection标签,可以让ST.DIO直接打印到SDK控制台。将单处理器的"Run & Debug"配置捆。绑在一起,它们就可以同时运行各自的软件。,SDK基于Eclipse的调试窗口可以让开发人员插入断点,并提供变量赋值和存储分配方面的信息。

XMD控制台

对我们来说,重要的XMD控制台命令是关于多处理器系统使用的命令。用帮助命令可以直接从XMD控制台调出这些命令的详细列表。为将XMD控制台用于多处理器系统的和调试,可使用命令connect mb mdm –debugdevice cpunr ,将处理器经由MicroBlaze调试模块(MDM)连接到XMD控制台。其中,参数用于定义每个处理器的标识符。在完成所有处理器的连接后,使用命令Target ,选择一个Microblaze用于处理当前的目标连接。"Target"命令可显示已连接目标的列表。要将。elf文件到特定的目标处理器上,开发人员可使用"dow"命令输入完整的路径和文件名:dow .用户既可以运行"run"命令启动被选中目标上的软件,也可以使用"stp"命令单步调试运行代码。如果MDM具有PLB连接XMD控制台,可使用命令Read_uart start输出JTAG UART.在定义端口后,JTAG UART服务器即可接收这些输出,并使本地主机上的输出可供终端程序使用(例如:HTerm或者Tera Term):Terminal jtag_uart_server .

流水线系统

我们逐步设计实现的双处理器平台系统,由两个得到Xilkernel支持的MicroBlaze处理器构成,它们通过FSL共享两个通信接口,并访问共享存储器。每个处理器都配置了运行在外部DDR2 SDRAM模块中独立存储区上的指令和数据高速缓存。而且,XPS Mutex模块能够对共享存储器访问进行同步,以保证数据一致性。此外,我们还为两个MicroBlaze调整了链接脚本,以便将专用存储区分配给两个处理器的指令段和存储段,以及一个共享数据段。

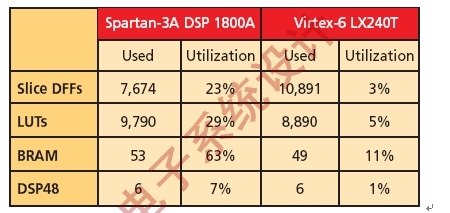

表1是在默认综合约束条件下,Spartan-3A DSP 1800A和Virtex-6 XC6VLX240T FPGA的资源分配和使用情况。即便是中等大小的Spartan器件,也能够为与双MicroBlaze系统PLB或FSL接口相连的额外加速器IP提供大量slice资源。

表1:双MicroBlaze Xilkernel系统的资源使用情况

这些尚未利用的FPGA资源,让我们能够为激光扫描仪的原始数据增加一个加速器处理单元。接下来我们的工作重点是,将基于QNX的防碰撞应用和线程任务分配给两个处理器。

由于障碍物识别、环境建模和远程控制构成了一系列的条件和顺序计算,所以我们选择了流水线处理系统。在今后的工作中,我们准备后续集成摄像头行车道检测功能,自动停放功能,以及其它所推荐的组件,比如:车辆测距和巡航控制。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 离心机的种类是什么2024/4/24 17:43:40

- 电路仿真软件哪个比较好?2024/4/23 17:50:46

- TCP/IP协议包括哪些协议2024/4/22 17:33:22

- cps是什么意思?cps的含义_cps的特征2024/4/16 17:56:11

- 你所知道的DCS系统都有哪些?2024/4/16 17:50:53