视频信号数字化光纤传输实验装置的研制

出处:tjsheep 发布于:2012-02-10 14:08:50

摘要:介绍了以FPGA为主控芯片,以光歼为通讯媒介的视频信号数字通信实验装置的设计实现过程,并对电路各个模块的功能及实现加以说明。电路在altium designer中设计完成,采用分模块式的设计,思路灵活,结构清晰,易于实现。在QuartusⅡ环境下用VerilogHDL语言进行编程并对程序进行仿真。该装置已做成了实物样本,实验使用表明:可以实现视频信号的传输,达到设计提出的教学要求和实际效果。

光纤以其频带宽、容量大、衰减小等优点给通信领域带来的改革和创新,形成了一个新兴产业。数字通信对比传统的模拟通信有抗干扰能力强、适用范围广、保密性能强、易于集成、功能稳定等优点。数字光纤通信兼有两者的优点,必将成为通信领域的发展方向。

视频信号的光纤传输有实时、准确、清晰的优点。在实验领域,可以快速准确地传递实验图像,给实验者更可靠的信息。在监控方面,可以实时传递监控图像,即节约成本,又有高的传输质量。因此,视频信号的光纤传输的研究与实现,将方便人们的学习、工作和生活。

本文是针对普通工科类高校中,非通信与信息工程等学科,具有普及性实验教学科目所研制的创新实验教学仪器。该实验仪器的推出,有利于帮助高等学校基础性学科实验课程的提升,丰富与完善实验课内容,使学生了解现代技术的发展与相关知识的掌握。

1 系统的硬件结构

整套装置由两大部分组成:光接收器和光发射器。两者之间以光纤连接。光发射器与光接收嚣的工作原理相互关联,一个是另一个的逆过程;光发射器是将视频的电信号转变成光信号,光接收器是将光信号转变成视频的电信号。

光发射器由滤波放大、A/D转换、控制部分、并/串转换、电/光模块部分组成。

光接收器由光/电转换部分、串/并转换、控制部分、D/A转换、模拟信号放大部分组成。

2 系统电路设计

2.1 电源

整套装置仅以7.5 V直流电源供电,内部集成电路需用到5V、1.5V、3.3V的电源。5V电源由L7805三态稳压电源提供,3.3V和1.5V分别由ASM117-3.3和ASM117-1.5提供。

2. 2 FPGA主控部分

电路采用型号为EPIC3144C8的FPGA为主控芯片,由32 MHz的晶振提供工作时钟。芯片共有4个时钟输入端,选其一输入晶振时钟。由于FPGA各个模块都用到,所以各个模块都需要供电和接地。

FPGA内部有两个锁相环,可以进行分频和倍频,以得到不同的频率。发射器中FPGA提供模数转换芯片和并/串转换芯片的时钟并将模数转换器输出的八位数据编码成十位数据传送给并串转换芯片,即完成8B10B编码和数据传输。接收器中FPGA提供数模转换器工作时钟和串并转换器的参考时钟,并将串并转换器输出的十位数据解码,还原为八位数据传输给数模转换器。FPGA的功能由Verilog编程实现,程序采用AS(主动)配置方式到FPGA.

2.3 视频信号的处理及采集

视频信号经滤波、放大、同步分离,由模数转换集成芯片采集转换成数字信号。

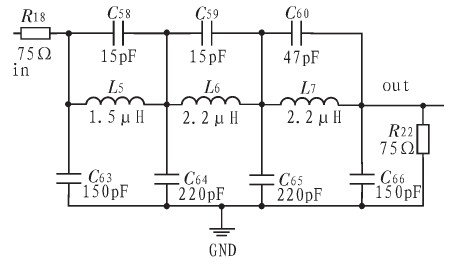

2.3.1 滤波放大部分

在对视频信号进行采样时,当信号中含有大于二分之一的采样频率,如果采样频率不够高,就会产生混叠信号。混叠信号不能用数字滤波方法除去,需要用硬件滤波。A/D转换的采样频率需要高于视频信号频率的2~10倍,为了在模数转换阶段不出现更高频率,即不出现混叠干扰信号,滤波需在A/D转换之前进行。根据所需视频信号的带宽以及抗混叠滤波所需要的特性,设计一个7级的低通滤波器,截止频率为6 MHz,电路如图1所示。

图1 视频滤波器电路图

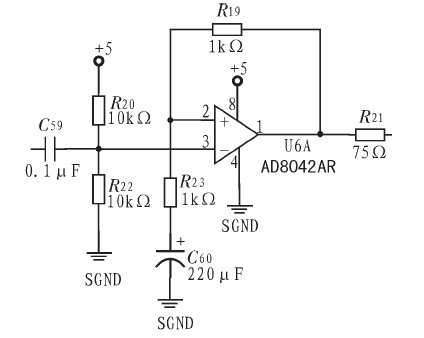

放大电路采用美国模拟器件公司出品的集成AD8042来实现。AD8042是一款功耗低、电压反馈型的高速放大器。它具有单电源供电能力,其0.1BD增益平坦度为14 MHz,采用5 V电源时的差分增益和相位误差分别为0.04%和0.06%.工作于5 V电源时,它具有160 MHz的带宽。低失真和快速建立特性使得它可以用于缓冲单电源和高速数模转换电路,电路如图2所示。

图2 视频放大器电路图

图中AD8042采用5 V电源供电,采用放大。

2.3.2 同步分离部分

全电视信号中除了图像信号外,还包含复合同步信号:由行、场和色副载波等组成;这些同步信号与图象、声音信号按照一定规格的国际制式编制标准构成,使得整个视频信号完整协调统一。所以在进行传输处理视频信号时,要对其中的同步信号实施技术分离,以便相应控制处理,具体电路采用LM1881集成芯片实现。该芯片可从全电视信号中提取与分离出:行和场、后延同步、奇偶场的图像信息。图像的复合视频信号直接由系统的相关设备提供,芯片的BACK PORCH管脚在视频信号消隐期间产生后延脉冲,该脚接到A/D转换器AD9280的CLAMP端口即19脚,使A/D转换器在信号的消隐期间处于钳位工作模式,可将消隐电平钳位在0电平的位置,从而使得采集处理信号时能够正确得把握各个信号间的时序关系和逻辑关系,完成同步信号分离的功能。

分离电路采用美国国家半导体器件公司出品的集成LM1881来实现,电路如图3所示。

图3 同步分离电路图

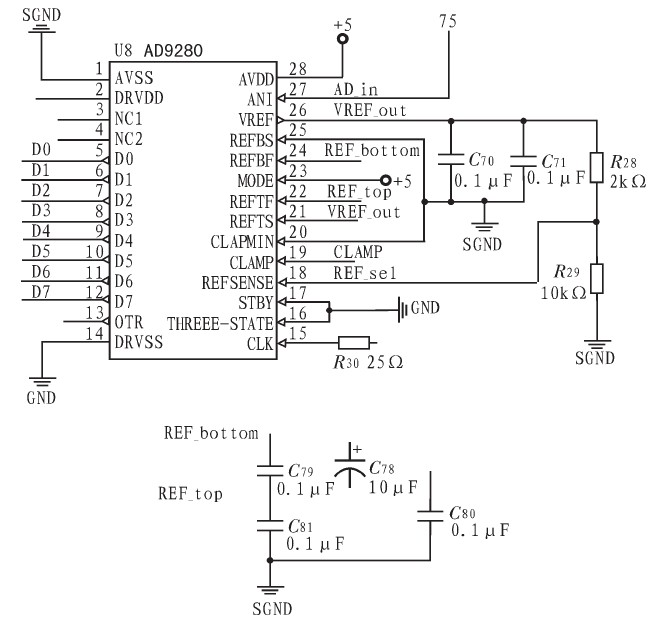

2.3.3 A/D转换部分

模数转换电路同样采用美国模拟器件公司出品的集成AD9280来实现,其工作时钟频率设定为32MHZ,由FPGA提供。信号由AIN管脚输入,D0~D7输出转换后的8位二进制数据。STBY和THREE-STATE脚接地,以保证芯片正常工作。CLAPMIN接地,把消隐电平钳位为0电平,其电路如图4所示。

图4 A/D转换电路

2.4 信号发送部分

由FPGA处理后的数据要通过光纤发送,不需先将并行数据转换为串行数据,再将串行数据转换为光信号。

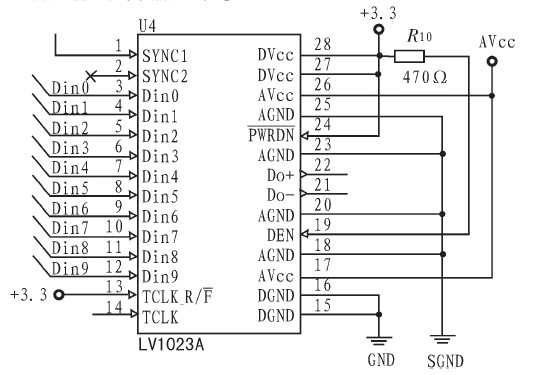

2.4.1 并/串转换

电路采用串化器DS92LV1023集成芯片实现,电路如图5所示,其对应接收端由解串器DS92LV1224集成芯片完成。DS92LV1023可以将10位并行数据转换为串行差分数据流,该差分数据流可以由DS92LV1224还原为10位的并行数据。这一组芯片内部有锁相环,可以为数据输出自己匹配时钟。串化器LV1023参考时钟选为32MHz,数据在该时钟频率下输入,其芯片内部匹配产生数据输出时钟,每一个10位并行数据转换为12位串行数据,其中多出一个起始位和一个终止位,所以有效频率为320 M.解串器的参考时钟定为16MHz,以满足数据传输需求。

图5 并/串转换电路图

由于视频信号是实时不断的,所产生的数据流连续进行,所以电路不能设置进入高阻态或省电模式,因此LV1023的DEN和PWRDN都置高电位。

串行数据的准确传输需妥串化器和解串器同步,该组芯片有2种同步方式:

1)快速同步 串化器LV1023发送一组同步信号,由连续是6个"1"和6个"0"组成,发送同步信号是由SYNC1和SYNC2控制的,当SYNC1或SYNC2置高电平持续时间超过6个时钟周期时,则开始连续发送同步信号,当解串器LV1224接收到同步信号后便开始试图锁定时钟信号,锁定完成之前LOCK保持高电平,锁定完成后LOCK跳变为低电平。

2)随机同步方式 该组芯片在没有同步信号传输的情况下仍然可以完成锁定,这使该组芯片在开放场合得到应用。随机同步时,串化器不发送同步信号,解串器直接对差分数据流进行锁定,该锁定方式会受到初始时数据和时钟的相位影响,也会受到数据本身的影响,当一个特殊的数据图样反复出现时,解串器可能出现锁定错误,称为RMT.但当同步丢失后,解串器会重新锁定时钟,恢复同步。

由于该电路采用随机同步方式。串化器的SYNC1和SYNC2悬空。

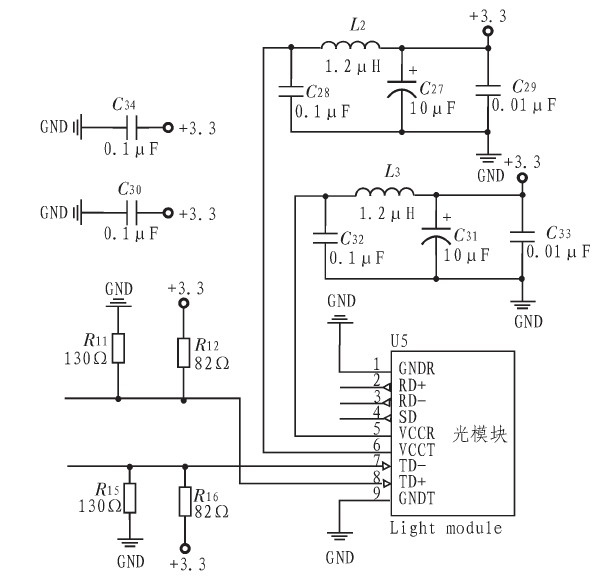

2. 4. 2 电/光模块

采用型号为HNMS-XEMC41XSC20,工作波长在T1310nm/R1550nm的单纤双向一体化收发模块,将电信号差分数据流转成光数据信号流,电路如图6所示。

图6 光发射模块电路图

2.5 信号的接收及处理

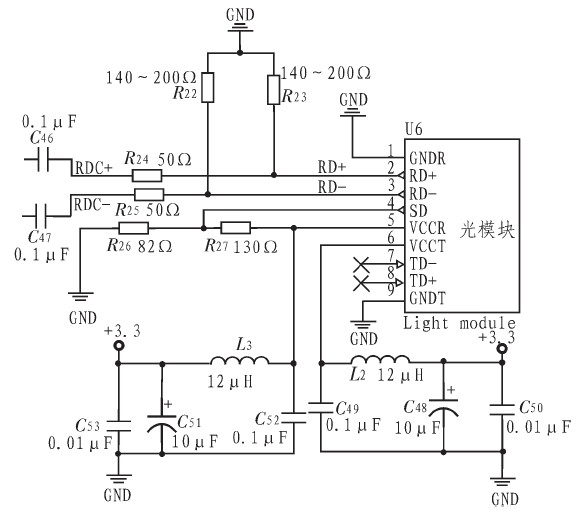

2.5.1 光/电转换模块

装置以单纤进行信号传输,光信号传输到接收装置后,需要还原为电信号,即差分电压数据流。采用型号为HNMS-XEMC41XSC20,工作波长在T1310 nm/R1550 nm的单纤双向一体化收发模块,将光信号转换为电信号。转换后的差分信号由RD+和RD-输出。电路如图7所示。

图7 光电转换电路图

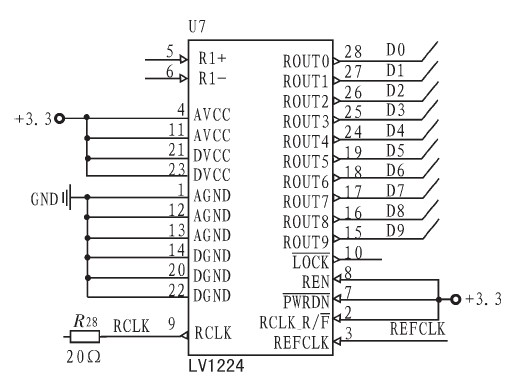

2. 5. 2 串并转换

装置采用与发送器中的串化器DS92LV1023相匹配的解串器DS92LV1224.发送器中的串化器将10位的并行数据转换为串行的差分数据流,因此在接收器中需用相应的解串器将串行差分数据流还原为并行数据。

DS92LV1224内部有锁相环,在接收数据流时可以根据数据的频率自行匹配接收时钟,外界只需为其提供参考时钟。此处参考时钟选为16MHz,由FPGA控制部分提供。芯片还匹配了与解串后的数据同步的时钟,以助于转换后的并行数据输出。参考时钟和数据输出时钟分别为REFCLK和RCLK引脚。为了保证视频信号的连续性和实时性,需避免芯片处于省电模式或高阻模式。因此PWRDN和REN需接高电平。RCLK-R/F接高电平,即选择时钟上升沿输出数据。

该组芯片有2种同步方式:快速同步和随机同步。快速同步是由串化器发送一组由连续的6个"1"和"0"组成的同步信号,解串器收到信号后锁定数据时钟,锁定完成之前LOCK保持高电平,同步完成后跳变为低电平。同步信号的发送是由串化器的SYNC1和SYNC2控制的,只要两者之一置高电平持续时间超过6个时钟周期,串化器就开始连续发送同步信号。快速同步具有快速准确的优点,但在长距离的信号传输中,光纤只传递数据,无法很好的传递串化器和解串器的SYNC和LOCK信号。因此采用随机同步方式。随机同步方式串化器不需发送同步信号,解串器直接对数据流进行锁定,实现同步,锁定丢失后,解串器会重新锁定时钟。将LOCK接到FPGA以进行实时控制。串/并转换电路如图8所示。

图8 串/并转换电路

2.6 D/A转换及视频信号输出

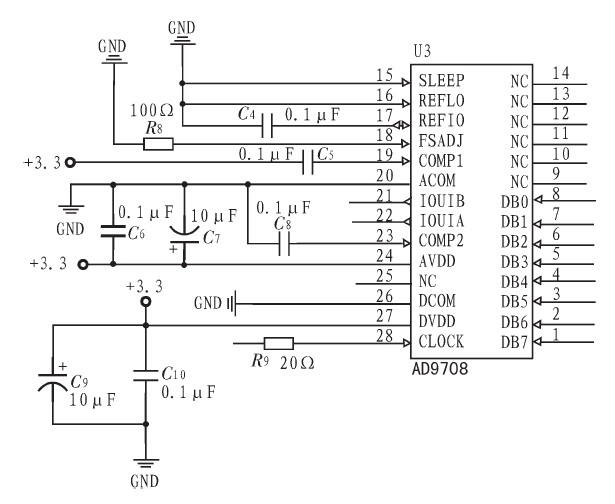

2.6.1 D/A转换部分

采用美国模拟器件公司出品的AD9708,它属于高性能、低功耗CMOS数模转换器,能提供出色的交流和直流性能,支持125 Mz/s的更新速率。工作时钟设为16 MHz,由FPGA提供。

AD9708的外围电路如图9所示。其中REFLO是转换基准的参考地,此脚接地禁用内部参考电压。COMP1是噪声衰减模式设置端,此处串接0.1 μF的电容能达到较好的转换效果。R9是终端匹配电阻以消除高频振荡。C9和C10用以滤除数字电源纹波,C6、C7用以滤除模拟电源纹波。并行数据由DB0~DB7输入,转换后的数据由IOUTA输出。此处输出的信号须经运放放大后,才能满足通用性视频显示器的技术要求。

图9 D/A转换电路

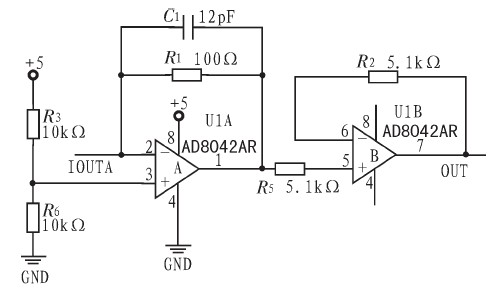

2.6.2 模拟放大及视频信号输出

采用AD8042实现信号的放大,如图10所示。ULA将AD9708输出的电流信号转换为电压信号,其中C1主要作用是去除高频干扰。ULB作为电压跟随器,用于阻抗匹配。要求的输出阻抗是75 Ω,电压跟随器使输出阻抗为0,再串联一个75 Ω(在ULB的7脚之后,图中未标出),来满足匹配要求。

图10 模拟放大电路图

3 程序设计及仿真

系统采用VerilogHDL语言进行程序编写,在QuartusⅡ环境下编辑仿真。FPGA内部时钟由32 MHz晶振提供。FPGA的工作是:1)提供D/A转换芯片AD9708、A/D转换芯片AD9280、并串转换芯片LV1023的工作时钟和串并转换芯片LV1224的参考时钟,都是16 MHz;2)发送端对数据进行8B10B编码,并将转换后的数据传送给串化器;接收端获取串并转换后的十位数据,进行解码,还原为编码前的八位数据,并将解码后的数据传送给数模转换芯片。

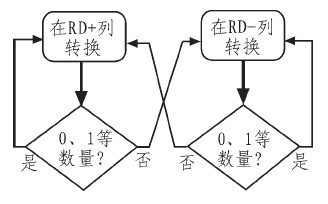

3.1 8B10B编解码

8B10B编码是目前高速串行通讯普遍采用的编码方式,8B10B编码的目的是将八位数据转换成10位的数据,并使转换后的数据流中"0"和"1"的数量平衡,避免发送过程中因过多重复的出现"0"或"1"而发生的错误,提高线路传输的性能,有利于接收器更准确的捕捉同步时钟,而且采用特定的码元可以使接受端更准确地对准码元。

8B10B编码可以看成是5B6B和3B4B编码的组合,组合过后有些编码可能有两个值,"1"和"0"的差值称为平衡度,用RD-表示平衡度为+2或0,RD+表示平衡度-2或0.将转换后的数据接平衡度分为RD-和RD+两列。设变量DISPIN表示正在转换的数的平衡度,DISPOUT表示下一个转换的数的平衡度。初始时设DISPIN与DISPOUT相等,先从RD-中开始转换,如果转换后的数"0"和"1"的数量相等,继续在RD-列中转换下一个数,如果"0"和"1"的数不等,则转到RD+列中转换。同理在RD+列中,如果"0"、"1"个数相等则继续在RD+中,否则换到RD-中。

解码部分将10位数据的前六位和后四位分别按照5B6B和3B4B的列表解码即可。

图11 8B10B编码流程

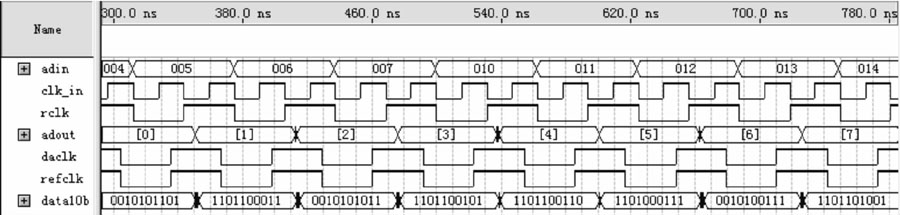

3.2 仿真

设计程序经QuartusⅡ综合器编译综合成功后,可以对输入数据、中间产生的数据、输出数据进行仿真。装置采用的8B10B编码方式,分为3B4B和5B6B进行编码。解码部分依照编码时相同的分发将十位数据分为4B和6B分别解码。解码后再按顺序组合成8位数据。程序以4B3B、6B5B分别查表的方式实现。

程序仿真图如图12所示,adin是编码之前的八位数据,设为逐次加一的计数数据,为了方便比较,图中用十进制表示。编码后的十位数据为data10b,adout是解码后的数据。可以看到虽有延迟,解码后数据仍为计数数据。因此程序可以准确地实现解码功能。

图12 程序仿真图

4 结束语

全电视信号中除了视频信号外,还包括音频信号,其声音信息的传输与转换处理,是应用领域中不可缺少的内容与完备。除了单向通信外,收发设备之间相互进行信息交换,实现双向通信、完成反向控制功能,在光纤通信应用领域中获得广泛应用和普及。这些课题的技术性拓展与转换,移植到相关实验教学的应用中,一定有其积极的作用和意义。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 煤矿人员定位系统的功能及重要性分析2024/4/16 17:43:54

- 什么是冗余?2024/4/15 17:33:02

- linuxfind命令详解2024/4/15 17:27:22

- 变压器容量和功率2024/4/12 17:42:41

- 什么是SSH端口号?SSH原理详解分析2024/4/11 17:52:00