差分滤波器布线需要注意的8个问题

出处:电子发烧友 发布于:2023-07-24 11:36:00

当提到通信系统时,比起单端电路,差分电路总是能提供更加优良的性能——它们具有更高的线性度、抗共模干扰信号性能等。使用差分电路的挑战就是抛开它们难于设计、测试和校正的想法,需要仔细观察如何使用差分滤波器。那么版主问一句,如何使用差分滤波器?你晓得伐?

不晓得,就继续往下看,版主简单明了的给你们说说8个需要注意的点儿~

1、 成对差分走线的长度须相同

此规则源自这一事实:差分接收器检测正负信号跨过彼此的点,即交越点。因此,信号须同时到达接收器才能正常工作。

2、差分对内的走线布线须彼此靠近

如果一对中的相邻线路之间的距离大于电介质厚度的2倍,则其间的耦合会很小。此规则也是基于差分信号相等但相反这一事实,如果外部噪声同等地干扰两个信号,则其影响会互相抵消。同样,如果走线并排布线,则差分信号在相邻导线中引起的任何干扰噪声都会被抵消。

3、同一差分对内的走线间距在全长范围内须保持不变

如果差分走线彼此靠近布线,它们将影响总阻抗。如果此间距在驱动器与接收器之间变化不定,则一路上会存在阻抗不匹配,导致反射。

4、差分对之间的间距应较宽

以使其间的串扰。

5、如果在同一层上使用铜皮铺地,应加大从差分走线到铜皮铺地之间的间隙

推荐间隙为走线宽度的3倍。

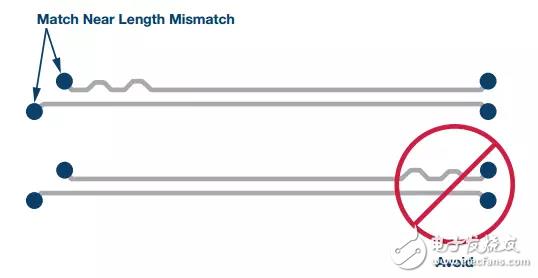

6、在靠近差分对内偏斜源处引入少量弯弯曲曲的校正

从而降低这种偏斜。

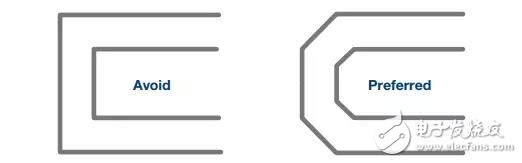

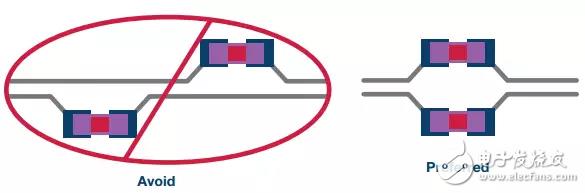

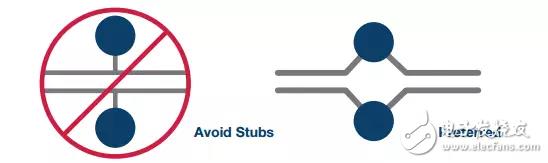

7、差分对布线时

应避免急转弯(90°)。

应使用对称布线。

若需要测试点,应避免引入走线分支,而且测试点应对称放置)。

8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。

与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。

上一篇:使用智能模拟模块进行设计

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- BiCMOS 运算放大器的知识2024/4/16 17:41:17

- 模数转换 – 性能标准2024/4/8 16:37:02

- 解析 PWM (DAC) 性能:第 4 部分 – 非均匀占空比组2024/3/28 17:23:37

- 了解运算放大器的输出信号摆幅2024/3/18 16:29:20

- 模拟和数字传感器和转换器2024/3/7 16:39:16