一种高可靠刀闸接口箱控制器的设计

出处:维库电子市场网 发布于:2017-11-23 16:00:00

数字化变电站的思想是设备智能化、信息互动化、控制网络化、功能一体化、状态可视化,终实现高可靠的坚强智能电网。数字化变电站与传统变电站相比在间隔层和设备之间增加了一个强大的过程层业务单元,可以把现有设备接入数字化变电站。过程层主要设备为智能接口单元:包含断路器操作箱和刀闸接口控制箱,本文介绍刀闸接口控制箱的实现。

刀闸接口箱用来控制隔离开关,其可靠性成为数字化站检修的关键部位,因此需要设计一种高可靠装置以防止带负荷拉、合隔离开关,带电合接地刀闸,带接地线(接地刀闸)合断路器(隔离开关)。装置还要满足智能控制、通讯以保障符合IEC61850标准运行。本文介绍利用双FPGA实现刀闸接口箱的高可靠性以及通讯控制的设计方法。

1 系统设计

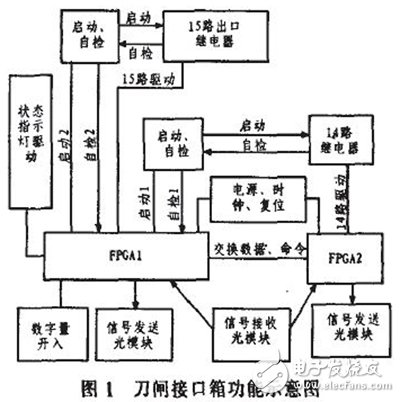

一个220 kV断路器需要7个隔离刀闸,一个隔离刀闸需要6个开关量采集点以及1组带闭锁的组合触点。6个开关量分别用于采集三相刀闸的的开和关位置信息。刀闸接口控制箱除实现上述功能外,还具备信号指示灯控制、多种自检功能、通讯控制、现场状态信号采集和上传、上级控制命令接收、解析、执行等,其功能框图如图1所示。为了实现高可靠性控制,逻辑上采用了双FPGA控制,驱动电路上采用独立双启动,采用多继电器“逻辑与”组合实现出口控制。防止刀闸检修时隔离开关误闭合导致人员伤亡事件发生。

1.1 硬件实现方案

数字量开入用于采集现场信号状态和逻辑控制硬压板,开入电路均具备一定的抗干扰能力;出口电路具备7路分闸、7路合闸以及7路闭锁用于执行相应的回路分闸与合闸。开入和出口均有强弱电隔离回路,能够保障4级快速瞬变和浪涌4级抗扰度实验。光收发通道用于实现远动控制,实现现场数据和装置状态量上传和接收控制命令,实现刀闸分合操作。还有14路指示灯用于指示分合闸位置和装置运行状态。装置还有一个CPU单元用于数据运算和解析执行命令。CPU单元与个FPGA之间通过串口交换数据,通过GPIO与第二个FPGA交换数据和命令。两块FPGA独立启动和出口;然后再把出口继电器触点进行逻辑组合实现更高等级的可靠传动。出口自检回路包括启动自检、击穿自检和断线自检。其中启动和断线故障立即报警,击穿故障时立即闭锁出口。硬件设计的为两块相同的FPGA,该装置的所有逻辑功能都是利用这两块FPGA芯片实现。该芯片选用XILINX的XC3S50AN,拥有50 k个系统门、1 584个逻辑单元、1 MbitFlashROM、65 KRAM、3个乘法器、2个DCM时钟管理器;可提供144个IO口。该芯片还具有低功耗、灵活的信号电平兼容性;内核1.2 V、IO为3.3 VTTL支持5 V容限输入。PU单元采用具备串口和GPIO的单元,限于篇幅这里不作介绍,本方案重点是采用先进的出口自检、启动以及出口逻辑组合;FPGA的系统设计方案:电源管理、复位电路、时钟分配以及FPGA配置电路的设计。

1.2 电源、复位及时钟系统的设计方案

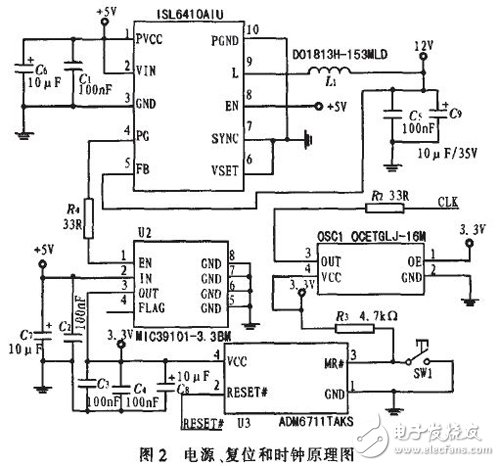

本装置需要以下等级电源:24 V电源为出口继电器提供驱动、5 V电源为光信号收发模块提供驱动、3.3 V电源为FPGA的IO、时钟电路提供驱动电源、1.2 V为FPGA内核提供工作电源。选用免维护的LAMDA电源模块HWS50/HD把直流220 V转换为+24 V;DC—DC模块PSS3—24—5把+24 V转换到+5 V。FPGA所需要的3.3 V和1.2 V则选用高效电源管理芯片ISL6410AIU和MIC39101—3.3BM,其实现方法如图2所示。U1-4脚为1.2 V电源建立完成标志,使用该信号控制U2-1脚3.3 V电源使能,保证内核电源可靠工作后再建立IO电源。L1为滤波电感器,应保证负载的通流能力,选用coilcraft公司的DO1813H—153MLD型号。选用高可靠性的集成电路ADM6711TAKS实现手动复位和电平门槛监视复位。复位输出信号PORESET#为低电平有效,保障整个系统可靠复位。选用epson公司的高低温漂晶体振荡器OCETGLJ-16 M,所需电源为3.3 V,输出时钟为16 MHz,连接到FPGA的全局时钟入口,可以直接驱动两个FPGA。

1.3 启动、出口及自检回路

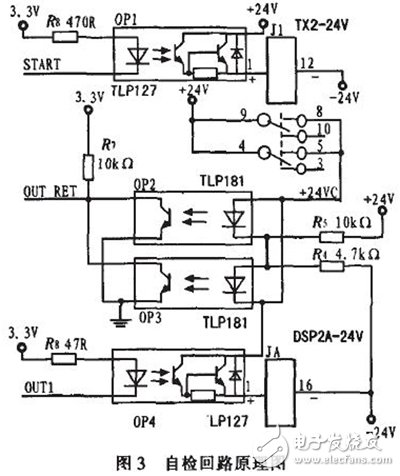

为了实现出口闭锁,设计了出口启动电路,只有出口电路和启动电路同时动作时才能把信号开出。为了防止电路故障而导致拒动,设计了启动及出口回路的自检电路如图3所示。两个FPGA各有一套完整的启动及自检回路,组合出口是利用两个FPGA驱动的继电器触点进行“逻辑与”后实现出口。启动自检方法:关闭出口信号(OUT1高电平),打开启动继电器(START低电平);OP1导通,J1动作+24VC接通24 V电源、OP2导通,OUT_RET变为低电平,实现启动自检。出口自检方法:关闭启动继电器(START高电平),打开出口(OUT1低电平);OP3、OP4导通,OUT_ RET变为低电平,实现出口回路自检。多路出口自检时,需要每一路轮流自检,由于可能会有干扰,可以通过设定某一路10轮自检均错误时才判定该回路故障。

2 FPGA编程

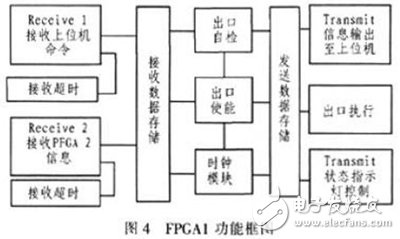

本方案由于没有主控单元(MCU),需要接受上位机的指令并执行相应功能。所以出口控制的实现都要依赖于FPGA,在每个FPGA中均设计启动和出口自检以及数据交换处理功能,功能如图4所示,第二块FPGA可以参考块设计,FPGA2通过串口把自己的状态提供给FPGA1,两块FPGA均是通过接收上位机的命令执行相应的功能。

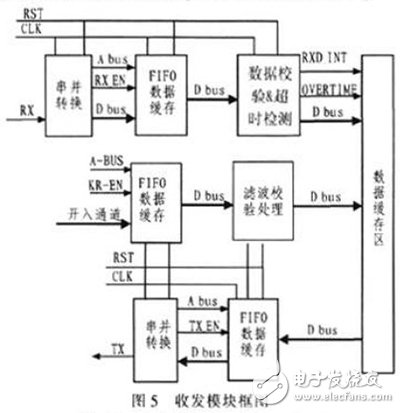

2.1 信息收发模块

信息收发模块:主要有命令接收、信息发送回路,在FPGA中做一个异步接收器、串并转换器件,把接收到的数据存入命令缓冲区。把现场的状态信息通过开入回路采集后存入状态缓冲区,当收到回传信息命令后把信息数据转换为串行格式通过光发送模块送出数据。功能框图如图5所示。

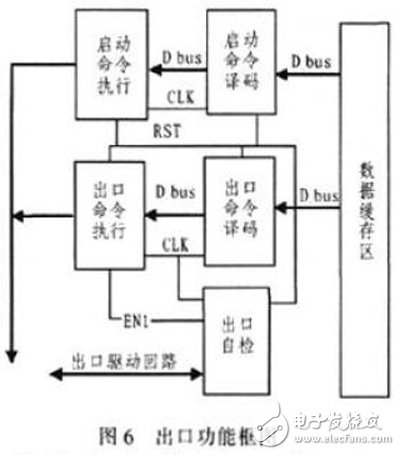

2.2 命令执行模块

命令执行模块包括:出口启动、出口使能、出口传动功能。命令执行电路读取存放在信息缓存中命令数据,接收到启动命令时,启动出口电源,为随时出口做准备,其间没有出口命令并且启动故障消失时,启动返回。当接收到出口命令时,执行出口命令;启动及出口命令发出后,通过硬件执行电路驱动隔离开关闭合或断开。并把执行结果存入状态信息缓存。功能框图如图6所示。

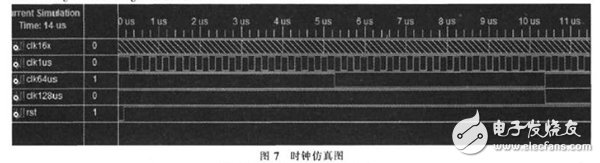

2.3 时钟生成模块

时钟生成模块在实现出口自检、使能时需要1μs、64μs和128μs的时钟,实现指示灯闪烁时需要500μs时钟。利用FPGA的DMC模块把16 MHz的时钟分成系统所需的时钟。时钟仿真图如图7所示。

2.4 软件实现方案及编程

软件编程按照分层模块的方式进行,采用常用的硬件编程语言VHDL;两块FPGA独立编译分别,保证逻辑和实现的独立性。编译环境为XILINX的软件ISE软件,版本号位10.3.1,该软件有非常强大的功能,具备很多常用的IP核,可以直接加载。自带仿真软件可以实现逻辑和时序仿真。配合XILINX的另一款逻辑分析软件chipscope可以在线探测芯片实际运行状态,测试逻辑和时序错误。综合使用软件能够快速实现系统设计。软件功能框图已经给出,限于篇幅VHDL语言的程序代码不再给出。

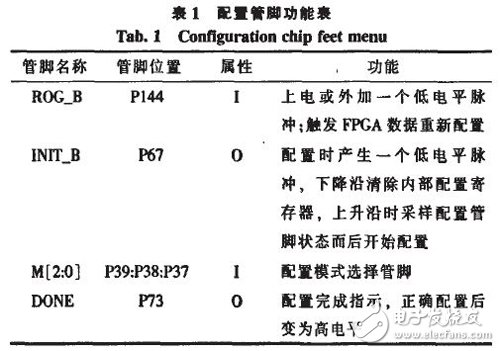

3 程序及配置方案

本系统两块FPGA全部使用ISP方案,利用FPGA的JTAG接口,把编程数据到内部的FLASMROM内。XC3S50AN的配置模式控制管脚M2、M1、M0决定FPGA引导配置数据的方法,计有8种。系统上电时,给PROG_B一个低电平,触发数据配置,在INIT_B低电平期间读取M2:M1:M0状态决定数据引导方式。本系统选用INTERNAL MASTER SPI MODE[0:1:1]。其中方便调试的JTAG MODE[1:0:1]可以支持JTAG口直接配置FPAG数据用于带电调试,当断电后数据丢失。XC3S50AN参与配置的管脚及功能如表1所示。

本设计为保证可靠性选用了2块FPGA同时工作,它们之间通过模拟串行口交换信息可以实现相互逻辑上闭锁。在电路出口处把2块FPGA驱动的继电器触点串联后作为终的出口控制,又在硬体电路上实现逻辑闭锁。如此可以保证装置的可靠动作,不会再有误动作发生。

4 整体测试

该方案设计的刀闸接口控制箱单元,已经制成产品调试成功,并完成型式试验。在数字化变电站试运行,运行中没有发现问题。测试环节进行了以下测试。

4.1 单板硬件测试

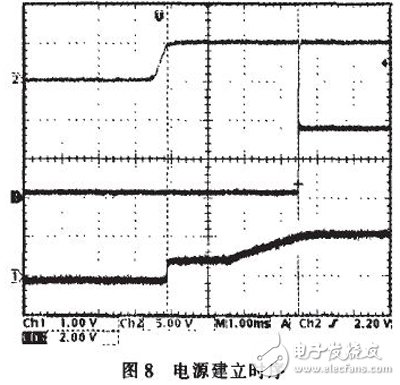

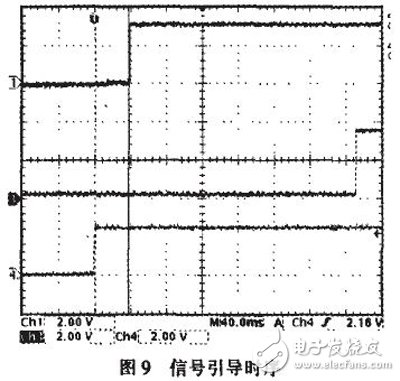

主要测试电源系统工作电压值及上电时序如图8所示,通道1至3分别为1.2、5、3.3 V电压建立波形,对于FPGA要求内核电源1.2 V建立完成后才能允许IO模块电源3.3 V建立。图9中通道4为3.3 V电源。通道1为FPGA程序引导完成信号DONE,DONE完成后FPGA内部逻辑可以正常工作。通道3为上电复位信号,该信号复位期间所有逻辑信号处在复位状态,完成复位后系统就可以正常工作了。

4.2 FPGA功能测试

一般通过仿真和黑盒测试两种方法,每一个功能模块可以通过设定边界条件测试功能完整性,整体逻辑功能一般通过测试输入信号和输出信号的逻辑关系,然后测试整套装置的功能完整性。

4.3 整装置功能和性能测试

整套装置按照设计技术指标测试功能和性能,主要测试了开关量动作值、动作时间、分辨率,光口通讯测试以及整装置环境适应性和EMC电磁兼容测试。均达到了设计要求,已经通过试验,满足现场运行条件。

5 结束语

由于方案应用了软体逻辑和出口驱动电路双重闭锁,使装置的运行可靠性有了很大提高,误动的可能性降到极小。测试和现场运行证明该方案是可靠的。该方案可推广到其他对动作可靠性要求高的场合。但是该方案为提高动作可靠性而增加了相对冗余的软件逻辑和硬件资源,必将提高系统制造成本。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 串联电路与并联电路的区分2024/4/25 17:15:00

- 查找隔离栅极驱动器的峰值电流2024/4/25 17:07:48

- 使用 GaN IC 离线电源的大容量电容器优化2024/4/24 17:30:57

- 并联电压电池2024/4/23 17:45:00

- 运算放大器压摆率和上升时间解释2024/4/22 16:16:53