用于MEMS陀螺的PCIe实时测控平台设计

出处:维库电子市场网 发布于:2017-12-25 16:07:21

微机电(MEMS)陀螺广泛应用于航空、汽车自动化和消费类电子产品等领域,按照振动结构的不同,主要分为线振动陀螺和旋转振动陀螺。随着MEMS陀螺成本功耗不断降低、体积重量逐渐减小,对其数字化方案也提出了新的要求如高、高采样频率等。为使MEMS陀螺能在高频率下工作,数字化电路就需要具备高采样频率,而目前MEMS陀螺的数字化主要是通过采用嵌入式现场可编程门陈列(FPGA)、数字信号处理器(DSP)芯片或者它们的组合来实现。

终使用MEMS陀螺在该平台上进行测试验证,使陀螺的信号解调和控制能在PC端实现,实际的使用过程比一般的FPGA或者DSP更加便捷。通过PCIe(PCIexpress)总线,实现PC和采集卡的高速传输,控制延时小于10μs.

1、计算机实时控制系统稳定低延迟优化设计

实时性作为陀螺测控系统的关键指标,本节将着重设计和优化控制系统的低延时性和稳定性。部分低延迟性优化主要包括硬件优化和软件优化。硬件优化需要考虑高速总线的类型和高速总线的传输控制方式;而软件优化则主要涉及到操作系统驱动层面的优化以及控制算法优化。第二部分稳定性优化是让计算机实时控制系统稳定地产生输出信号,在实际工程中则是避免该系统对陀螺设备的控制受到中断延时和传输延时波动的影响。

1.1、数据传输的低延优化

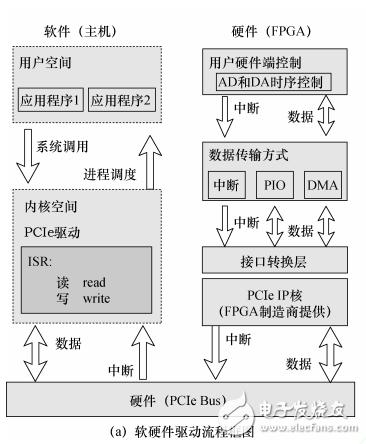

图1 实时测控平台低延迟优化方案

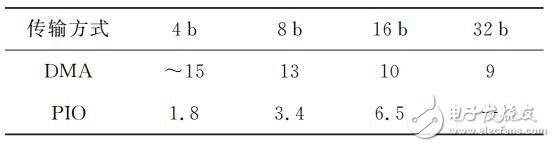

图1a展示了实时测控平台的软硬件框架和数据流向。硬件中断发出后,AD采集到的数据需要经过接口转换层、FPGA的PCIeIP核、PCIe总线等才能到达计算机IO内存空间。完成内存地址映射后,用户程序就可以从该内存读取数据,进行数据处理。在实际多线程的数据传输中,还会产生额外的延时,如图1b中所示,有中断延时、线程延时和线程上下文切换延时等。其中中断延时定义为计算机端硬件中断产生到中断服务程序(ISR)中条指令执行的时间差,主要与内核架构、CPU主频和负载有关。由于线程之间的调度,内核需要准备时间,用于保存和恢复线程上下文环境、获取或释放信号量等。线程延时定义为ISR中从产生唤醒正在等待的线程信号,到线程执行条指令的时间差。线程上下文切换时间则为一个线程运行完到第二个线程条指令执行的时间差。

考虑到本实时测控平台的数据量小,数据处理耗时短的特点,因此将陀螺控制代码全部在内核ISR中完成,从而消除了线程延时和线程上下文切换所耗费的时间,同时也间接消除了用户空间和内核空间数据传输的耗时,以此来满足数据的高速传输,如图1c所示。

图1.1 实时测控平台低延迟优化方案

为了实现数据低延迟传输,下文将具体针对系统总线、传输控制方式、驱动程序(硬件和软件)、数据处理等逐个进行优化。

1)高速总线的类型优化。

在测控系统中,总线是采集卡和计算机之间的桥梁,而总线的速度、带宽等因素对系统的性能至关重要。本测控系统高速可靠的数据采集和传输依赖于计算机和采集卡之间的传输效率,因此选择合适的总线可为后续板卡的进阶优化提供保证。随着计算机技术发展,总线技术也在不断革新,应用范围也从低、中速IO设备逐渐扩大到中高速设备。

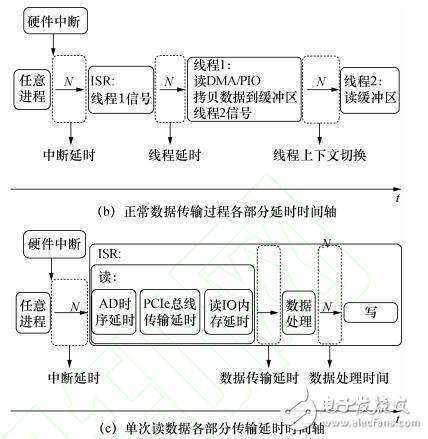

为了验证不同总线在不同PC平台下实际的传输速率,此处测试了4种情况(仅对目前已有的测试平台):DOS系统下的PC104总线、WindowsXP下的PCI总线、Windows7以及Linux(内核4.2)下的PCIe总线。其中本测试平台的ISA总线和PCI总线挂在相应的桥接芯片上,Windows7下的PCIe驱动是采用Jungo公司的Windriver工具自动生成的标准代码。结果如表1所示。

表1 不同PC总线的IO读写延时测试

表1中“W+R-8b”代表读和写一个8位的数,“W+R-32b”代表读和写一个32位的数。通过测试发现,PCIe总线在传输速率上优于PC104和PCI总线。对于不同系统下PCIe总线的延时结果显示,Windows下IO读写各1字节延时,耗时已达到15μs,而Linux下IO读写各4字节都只需1.8μs,原因是:Linux系统的实时性优于Windows系统的;另外,Windows下的驱动是Windriver工具自动生成的,并没有针对性的进行过优化。后文中的测试结果都是在Linux系统下完成。

2)传输控制方式优化。

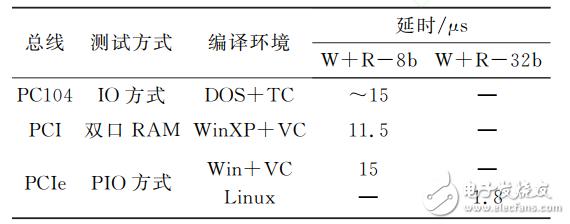

该测控平台要求单次传输的数据量虽然比较少,但采样频率较高,对测控系统的动态响应能力提出了较高的要求。为满足以上要求,需要一种快速的数据传输方式,常见的PCIe总线数据传输方式是PIO(programmedinput/output)和DMA(directmemoryaccess).DMA方式因不需要依赖CPU过量的中断负载,一般在处理图像等大数据传输中广泛应用,但是在对小数据量高速、高动态响应的情况下,却无法保证数据传输的及时性。

测试结果如表2所示,在Linux下,DMA方式读16字节的数据,传输时间就已经超过了10μs.而PIO方式能实现小数据量高速传输,更适合本测控平台。但是还需要对PC端PCIe驱动进一步优化,保证实时性。

表2 DMA和PIO传输时间对比

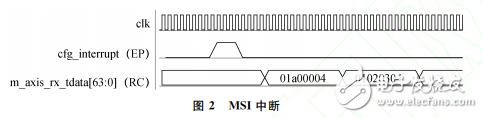

另外,PC和采集卡通讯有2种常见的方式:一种方式是轮询状态寄存器,另一种方式是使用中断。当轮询频率过快的情况下,PC负载也会大,此时无法保证CPU能及时响应,必然会产生较大的延时;而中断方式能明显缓解PC负载过重的情况。硬件中,外围芯片FPGA中的PCIeIP核支持两种不同的中断方式:MSI中断和Legacy中断.MSI中断是基于消息机制的,相比Legacy中断更高效更快速。为此,在FPGA中单独编写了一个中断处理模块,就能实现将硬件的MSI中断请求通过PCIe总线发送到PC端。下文搭建了一个产生MSI控制信号的仿真环境,对MSI中断进行了仿真验证。模拟仿真了两个设备:RC(RootComplex)和EP(EndPointDevice),分别由PC机和PCIe板卡模拟,仿真结果如图2所示。

图2中,cfg_interrupt为EndPointDevice产生的中断信号,中断发生后,RootComplex接收到数据包m_axis_rx_tdata,其中01a00004为消息头,数据为0x01020304.

3)PC端PCIe驱动优化。

通常情况下,内核层PCIe驱动编写好以后,开发者会给用户提供一个通用的应用库,用户可以在用户层完成相关算法的编写,方便研究人员更快速地进行开发工作。考虑到用户层权限低,用户和内核空间的数据传输存在延时会影响系统稳定性,降低数据传输速率。因此,本平台将控制算法的实现搬移到内核层,同时也给用户提供了一个相应的库,方便用户修改控制算法中的参数。

4)控制算法的优化。

前面提到算法在内核层实现,陀螺闭环控制中,需要产生正弦余弦信号。为了解决内核浮点兼容性和减少指令计算时间,本平台采用查表的方式,自制了一个正余弦表,将浮点运算转换为定点运算。因为PC机CPU主频高,所以查表的方式也能加速代码的运行。

1.2、稳定的实时数据传输设计

低延迟优化能使数据在短时间里从硬件传输到PC端。但是由于PC安装的是多任务的操作系统,无法保证每次都能在一个周期的同一个时间点响应中断,这一特性决定了这个短时间不是一个固定值,而是一个范围。在实际中,取值不定的这个短时间会引发数据传输的不稳定,从而导致对陀螺的控制不连续。

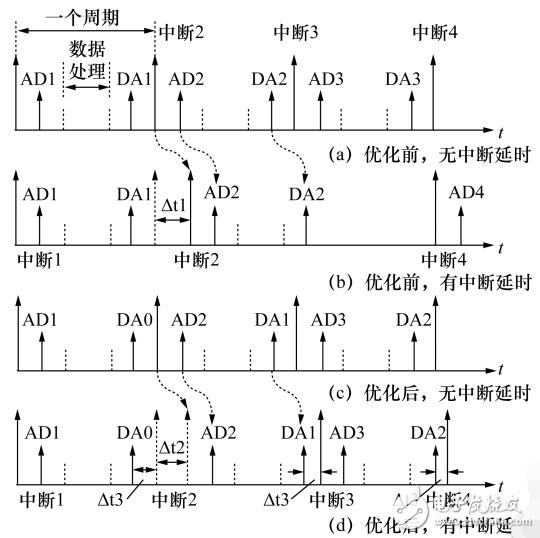

针对陀螺控制的不连续问题,以中断延时为例,分析了由该现象产生的负面影响,并设计了一套可靠的控制时序,如图3所示。假设它们都发生在ISR中,在一个周期中,进中断函数后,先读取下位机中AD的数据,进行数据处理,将解析完的数据再经过总线返回DA的值。图3a表示在中断和传输延时都固定时,正常的数据传输过程。而实际应用中,中断和传输延时都会波动。以中断延时为例,图3b中第二个中断信号到达时,假设已延时△t1,后续的读写操作相应的也会延迟△t1.当FPGA(下位机)往DA2寄存器写数据的时刻,写入的是上一周期中的DA1里的值,因为PC端并没有及时返回DA2的值(延时△t1),导致数据没有实时更新;另外,还有丢失中断的可能性,如图3b中的中断3.这两个问题都将加大陀螺控制的不稳定性。

图3 数据传输控制时序优化

由此可知,为了达到陀螺数据传输的稳定性和可靠性要求,除了要优化MSI中断控制方式和PIO方式传输方式,还需要上位机即PC和下位机即FPGA之间制定一套高效的握手协议。

2、陀螺控制系统

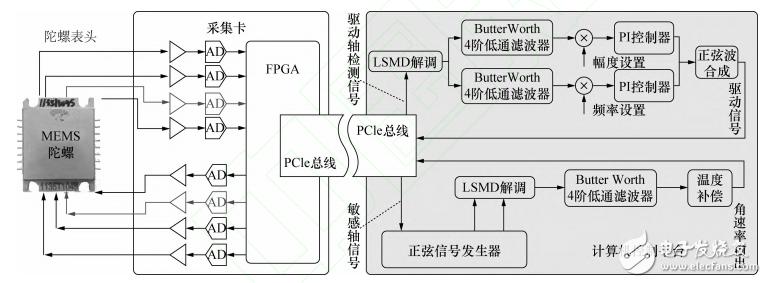

根据陀螺的工作原理,陀螺数字控制系统详细的总框图如图4所示。陀螺数字控制系统由4个部分组成:陀螺表头(包括前置处理电路)、ADC与DAC调理电路及FPGA外围电路、系统总线PCIe的控制和PC端的陀螺控制算法。

图4 完整的系统框图

第1部分是和陀螺直接连接的前置放大电路,前置电路产生陀螺的驱动电压并对陀螺输出的信号做初步的放大处理,用于提高信号的信噪比。

第2部分是AD和DA数据采集卡。由于既要采集AD的数据和控制DA的数据输出,又要与PC端进行高速的通讯,在这里采用能支持PCIe2.0的XilinxArTIx7FPGA,FPGA大大简化了数字电路的设计难度,便捷地处理AD和DA的时序还能提升PCB板的集成度。需要注意的是,这里的FPGA主要用于简化数字电路的设计以及实现和计算机进行高速通信,并不涉及陀螺控制信号的处理。

第3部分是FPGA和PC进行高速通讯的PCIe总线。

第4部分则是PC端的陀螺算法实现,

主要包括陀螺驱动轴频率闭环和幅度闭环控制。经过LSMD(leastsquaredmeandifference,均方差)解调以后的驱动轴检测信号分为正交分量和同相分量:其中正交分量与参考信号有90°的相位差,可以近似反映陀螺本身的幅值信息;而同向分量与参考信号同相位,可以近似反映陀螺本身的相位信息。低通滤波用于除去二倍频分量,在实际的闭环过程中,首先给陀螺驱动轴频率设定一个预估值,此时陀螺的驱动轴检测信号和驱动信号相位差接近-90°,并通过PI控制器作为反馈量,闭环控制驱动轴的输入频率,终使其稳定在谐振频率。

3、实验结果及分析

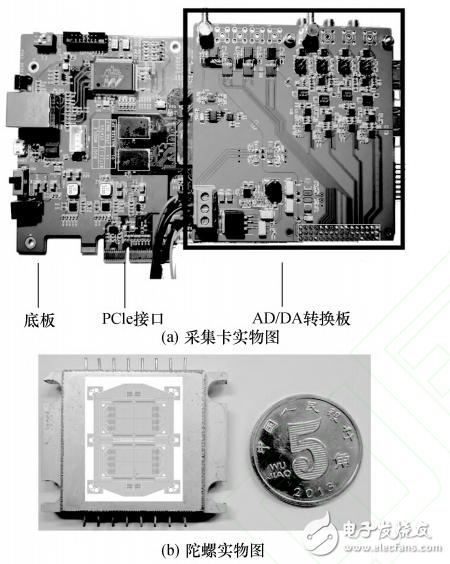

图5a为PCIe的采集板卡:底板上主要是XilGinxArTIx7芯片和PCIe的接口,主要功能是用于简化外围电路和PCIe总线的逻辑控制;AD/DA转换板上是AD和DA的调理电路,用于高陀螺信号的采集和控制信号的发生。图5b是用于测试的MEMS陀螺。

图5 采集卡和实际用陀螺

3.1、总延时时间消耗分布测试

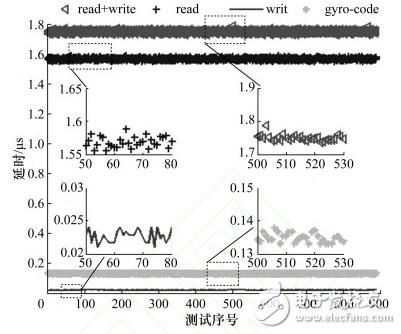

为了进一步了解程序运行时各部分功能所占用的时间,对数据读写以及代码量进行了延时测试。图6中,“read”代表PC端读4字节所占用的时间,“write”代表PC端写4字节到板卡所占用的时间,“read+write”代表读和写各4字节所占用的时间,“gyroGcode”代表单轴陀螺代码(小于1000条指令)运行占用的时间。

图6 传输耗时分布图

3.2、陀螺控制测试结果

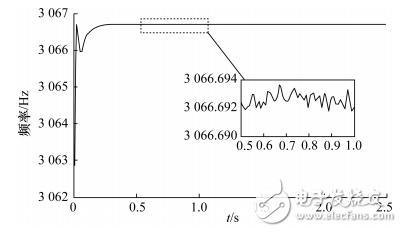

为了验证测控平台的可行性,本系统对陀螺控制程序进行简化,仅有陀螺驱动轴闭环控制(包括幅值闭环和频率闭环控制),检测轴开环,无自补偿环路。实测的频率闭环控制过渡过程如图7所示,大概在0.3s以后,驱动频率终稳定在3067Hz,频率闭环控制达到了很好的控制效果。

图 7 频率闭环控制曲线

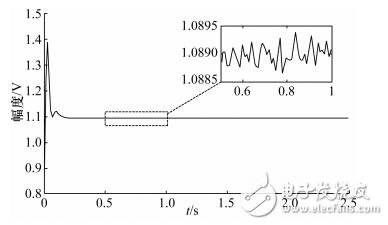

实测的幅值闭环控制过渡过程如图8所示,幅值终稳定在1V左右,与设定值相符

图8 幅度闭环控制曲线

4、结论

本文提出了一个用于MEMS陀螺的PCIe实时测控平台。通过硬件和软件优化,减少数据传输延时,并且利用高效的数据传输时序,实现了陀螺驱动频率闭环和幅度闭环控制,使线振动陀螺工作在谐振频率上且幅值稳定,终将测控系统的数据传输延时降低至10μs.下一步将通过优化实时内核,提高该测控系统的采样频率,为更高工作频率的陀螺提供高速、可靠、稳定的数据传输方案.

上一篇:传感器故障原因及解决方法

下一篇:工业物联网智能网关应用方案

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- DHT11传感器简介及数据传输过程2024/3/20 17:23:57

- 什么是DS18B20温度传感器,DS18B20温度传感器的优缺点2024/2/26 17:15:41

- 使用细铜线作为集成传感器和加热器进行温度控制2024/2/18 16:11:54

- 使用电感器改进现有设计2024/1/22 16:42:19

- 什么是SLAM?SLAM算法涉及的4要素2024/1/17 16:35:15