关于反熔丝FPGA的结构和原理以及其在密码芯片设计中的运用浅析

出处:电子发烧友网 发布于:2023-07-17 17:34:57

1 引言

随着计算机和通信的发展,信息传输过程中信息安全的重要性越来越受到人们的重视。在信息传输过程中,人们普遍采用将待传输的信息加密进行传输,然后在收端进行解密还原信息。对信息的加解密通常采用两种方法:软件加解密和硬件加解密。软件加解密实现简单,但须对密码算法进行多重保护存放且加解密速度较慢,而硬件加解密可加快加解密运行速度。在当今信息网络化的环境下,对加密的速度要求将越来越高,如:在ATM、帧中继、ISDN PRI等领域的加密,将会有数兆或数十兆以上的速度要求,所以硬件加密将是今后的加密手段。目前运用的硬件加解密,大都采用SRAM型的FPGA实现,必须外挂一EEPROM存储加载FPGA的数据,这就为信息安全带来了巨大隐患,特别是在运用于军事、政府等部门的保密通信产品中。要求重要信息不得以明文的形式出现。另外,SRAM型FPGA速度较慢,延迟时间不定,也大大限制了它们在一些特殊场合下的运用。

2 反熔丝FPGA的结构和原理

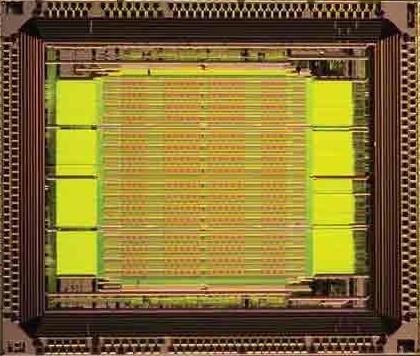

曾经,人们为了保护芯片中的内容不能读出而采取定制或半定制的办法,但这种方法生产周期长、不适合小批量生产。反熔丝FPGA的出现解决了人们的苦恼,大大方便了这种特殊应用的需要。目前,生产反熔丝FPGA芯片的厂家有QUICKLOGIC、ACTEL等几家。其中,QUICKLOGIC公司的反熔丝FPGA在我国开始大规模应用。

QUICKLOGIC公司的ViaLink反熔丝(Antifuse)结构是由四层金属层和中间的覆盖硅的钨通道组成。覆盖硅的钨通道具有高电阻和高电容特性,起到金属层之间绝缘层的作用,其电阻大于1千兆欧姆。但当编程电压作用于被选择的覆盖硅的钨通道时,硅将转变成低电阻连接,其电阻小于50Ω。因为这种结构不同于SRAM型的FPGA,它没有配置存储器,因此

编程内容是不可能被读出的,正是该种特性使得该系列芯片在保密通信领域具有广泛的应用前景。

反熔丝FPGA对于大多数设计可提供实现较好的性能,这是由于其可编程链路的电阻较小(反熔丝接点电阻50Ω左右),具有较好的布线灵活性,不会妨碍信号传送,并以直接

的通路进行,因而可大大提高芯片速度。众所周知,随着工艺的改进,SRAM型FPGA其触发器翻转速度已经做得很高,而芯片的速度仍然受限,其原因是信号在芯片内传输过程中所

耗时间占整个时延的60%左右,这就限制了整个芯片的速度。

目前,虽然反熔丝FPGA单片密度较SRAM FPGA的单片密度低,但对于大多数反熔丝FPGA在如下方面仍占的地位:布线结构的灵活性,使软件工具能够较容易的实现自动的布局、布线,且修改设计时,即使重新布线也可保持原配置的输出管脚不变。同时,在反熔丝FPGA之中的设计修改通常能保证在时延上变化很少,这是因为布线改变时所需的附加的可编程链路的时延增加不多。另外,反熔丝FPGA还具有功耗低、抗辐射能力强,耐高低温等优点。

因此,反熔丝FPGA的特性使得其在保密通信产品中具有特殊的应用。充分利用反熔丝FPGA的特性,可提高密码算法芯片的加解密速度,同时利用反熔丝FPGA的编程内容不能读出,保护密码模块中的主算法,避免了其他的物理保护,从而提高了系统的安全性。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- DDR 5,新标准发布2024/4/22 11:00:19

- dsp芯片作用及应用2024/4/16 17:46:38

- dsp芯片和arm芯片在技术有哪些区别2024/4/15 17:31:11

- L298N中文资料汇总_L298N引脚图及功能2024/4/12 17:34:41

- 双路差动比较器lm393工作原理2024/3/25 17:10:54