CMOS电路的ESD保护结构设计

出处:电子发烧友 发布于:2019-04-09 14:21:17

1 引言

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

2 ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

3 CMOS电路ESD保护结构的设计

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路 ESD电流,且能立即有效地箝位保护电路电压。而在这两部分正常工作时,不影响电路的正常工作。

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。由于MOS管与CMOS工艺兼容性好,因此常采用MOS管构造保护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管开启时能吸收大量的电流。利用这一现象可在较小面积内设计出较高ESD耐压值的保护电路,其中典型的器件结构就是栅极接地NMOS(GGNMOS,GateGroundedNMOS)。

在正常工作情况下,NMOS横向晶体管不会导通。当ESD发生时,漏极和衬底的耗尽区将发生雪崩,并伴随着电子空穴对的产生。一部分产生的空穴被源极吸收,其余的流过衬底。由于衬底电阻Rsub的存在,使衬底电压提高。当衬底和源之间的PN结正偏时,电子就从源发射进入衬底。这些电子在源漏之间电场的作用下,被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,终使NMOS晶体管发生二次击穿,此时的击穿不再可逆,则NMOS管损坏。

为了进一步降低输出驱动上NMOS在ESD时两端的电压,可在ESD保护器件与GGNMOS之间加一个电阻。这个电阻不能影响工作信号,因此不能太大。画版图时通常采用多晶硅(poly)电阻。

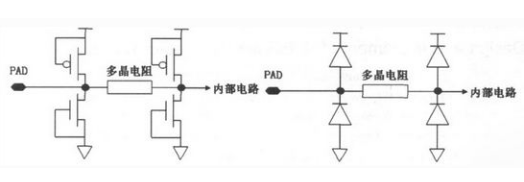

只采用ESD保护,在大ESD电流时,电路内部的管子还是有可能被击穿。GGNMOS导通,由于ESD电流很大,衬底和金属连线上的电阻都不能忽略,此时GGNMOS并不能箝位住输入接收端栅电压,因为让输入接收端栅氧化硅层的电压达到击穿电压的是GGNMOS与输入接收端衬底间的IR压降。为避免这种情况,可在输入接收端附近加一个小尺寸GGNMOS进行二级ESD保护,用它来箝位输入接收端栅电压,如图1所示。

CMOS电路的ESD保护结构设计

如果PAD仅作为输出,保护电阻和栅短接地的NMOS就不需要了,其输出级大尺寸的PMOS和NMOS器件本身便可充当ESD防护器件来用,一般输出级都有双保护环,这样可以防止发生闩锁。

在全芯片的ESD结构设计时,注意遵循以下原则:

(1)外围VDD、VSS走线尽可能宽,减小走线上的电阻;(2)设计一种 VDD-VSS之间的电压箝位结构,且在发生ESD时能提供VDD-VSS直接低阻抗电流泄放通道。对于面积较大的电路,在芯片的四周各放置一个这样的结构,若有可能,在芯片外围放置多个VDD、VSS的PAD,也可以增强整体电路的抗ESD能力;(3)外围保护结构的电源及地的走线尽量与内部走线分开,外围ESD保护结构尽量做到均匀设计,避免版图设计上出现ESD薄弱环节;(4)ESD保护结构的设计要在电路的ESD性能、芯片面积、保护结构对电路特性的影响如输入信号完整性、电路速度、输出驱动能力等进行平衡考虑设计,还需要考虑工艺的容差,使电路设计达到化;(5)在实际设计的一些电路中,有时没有直接的VDD-VSS电压箝位保护结构,此时,VDD-VSS之间的电压箝位及ESD电流泄放主要利用全芯片整个电路的阱与衬底的接触空间。所以在外围电路要尽可能多地增加阱与衬底的接触,且N+P+的间距一致。若有空间,则在VDD、VSS的PAD旁边及四周增加VDD-VSS电压箝位保护结构,这样不仅增强了VDD-VSS模式下的抗ESD能力,也增强了I/O-I/O模式下的抗ESD能力。

一般只要有了上述的大致原则,在与芯片面积折中的考虑下,一般亚微米CMOS电路的抗ESD电压可达到2500V以上,已经可以满足商用民品电路设计的ESD可靠性要求。

对于深亚微米超大规模CMOS IC的ESD结构设计,常规的ESD保护结构通常不再使用了,通常大多是深亚微米工艺的Foundry生产线都有自己外围标准的ESD结构提供,有严格标准的ESD结构设计规则等,设计师只需调用其结构就可以了,这可使芯片设计师把更多精力放在电路 本身的功能、性能等方面的设计。

4 结束语

ESD保护设计随着CMOS工艺水平的提高而越来越困难,ESD保护已经不单是输入脚或输出脚的ESD保护设计问题,而是全芯片的静电防护问题。

芯片里每一个I/O电路中都需要建立相应的ESD保护电路,此外还要从整个芯片全盘考虑,采用整片(whole-chip)防护结构是一个好的选择,也能节省I/OPAD上ESD元件的面积。

上一篇:电源模块的分类及特点

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 并联电压电池2024/4/23 17:45:00

- 运算放大器压摆率和上升时间解释2024/4/22 16:16:53

- B 类放大器的组成及其特性概述2024/4/16 17:22:23

- GaN 基高频 LLC 谐振转换器的设计注意事项2024/4/15 17:21:58

- 设计隔离降压转换器时如何选择变压器2024/4/15 17:05:28