PCB设计信号线跨分割会有什么影响

出处:面包板 发布于:2020-03-04 15:13:01

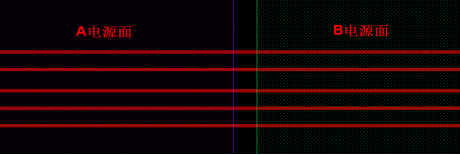

我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:

会导致走线的的阻抗不连续;

容易使信号之间发生串扰;

会引发信号之间的反射;

增大电流的环路面积、加大环路电感,使输出的波形容易振荡;

增加向空间的辐射干扰,同时容易受到空间磁场的影响;

加大与板上的其它电路产生磁场耦合的可能性;

环路电感上的高频压降构成共模辐射源,并通过外接电缆产生共模辐射。

编辑

图1-52 跨分割现象示意图

1.84 什么是ICT测试点,设计要求有哪些?

答:ICT,In Circuit Tester,自动在线测试仪,是印制电路板生产中重要的测试设备,用于焊接后快速测试元器件的焊接质量,迅速定位到焊接不良的引脚,以便及时进行补焊。在PCB设计中,就需要在设计中添加用于ICT测试的焊盘。ICT测试可以检测的内容有:线路的开短路、线路不良、元器件的缺件、错件、元器件的缺陷、焊接不良等,并能够并能够明确指出缺点的所在位置。

一般来说,ICT常用的设计要求如下所示:

ICT测试点焊盘大小直径为40mil,不小于32mil;

测试点或者固定孔不能被障碍物挡,不能添加在元器件里面;

ICT测试的是信号网络,尽可能多地覆盖网络,100%的网络,严格的会对器 件的空管脚也进行ICT测试;

测试点尽量在同一面,可以减小测试成本;

可用作测试的点包括:专用的测试焊盘、元器件管脚(常见的是通孔)、过孔;

测试点的测试焊盘要阻焊开窗;

测试点中心间距尽量不小于50mil,过近测试难度大,成本高;

测试点到PCB板边的距离有一定的要求,推荐为100mil,少要50mil。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PCB的基础知识,PCB常用基材2024/1/17 16:41:05

- 如何在定制 PCB 上设计精确的倾角计2023/11/24 15:50:52

- 通过 PCB 设计最佳实践减轻噪声2023/11/14 17:30:55

- 返工 PCB 电路板的 6 个技巧2023/11/9 16:28:27

- 四层板的常见 PCB 叠层2023/11/1 16:44:03