时钟切换电路及其注意事项

出处:电子市场 发布于:2017-07-13 16:51:48 | 3980 次阅读

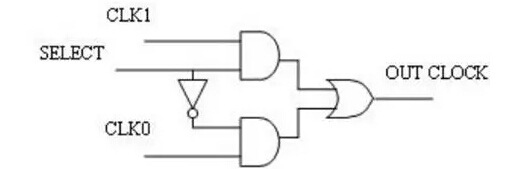

时钟同步问题讲完了,下面就开始讲讲soc中另一种常见的情况,有时为了考虑到功耗,性能的问题,某个模块可能在某一种情况下工作在一个频率,另一种情况下工作在另一种频率,这个时候就需要进行mux的切换,有的人就会说了,哪简单啊,加个mux啊,可事实真的如此吗?

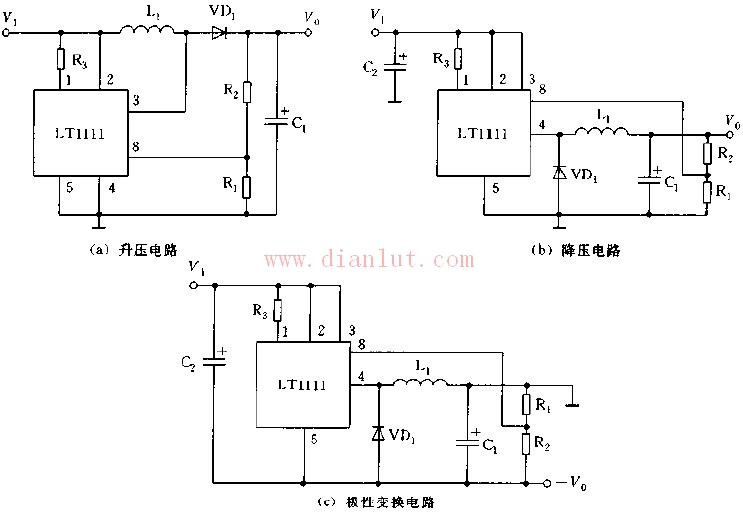

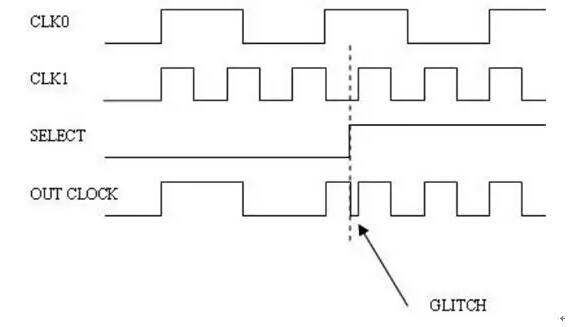

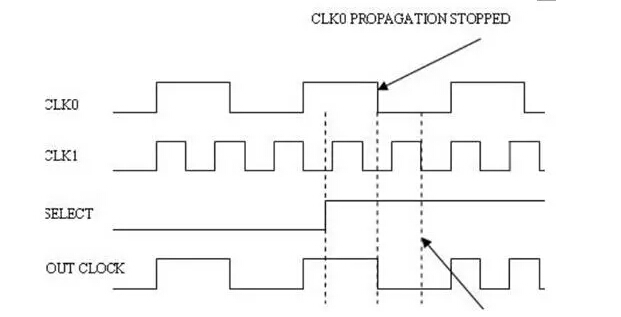

如上图,大家会很自然而想到的一种时钟切换电路,可是,你仔细分析,你会发现该电路会出现如下的问题,毛刺!这个毛刺无论对于clk0还是clk1都不是好事,它不属于任何一个时钟域,它的脉宽根本无法确定,你切换的点会影响毛刺的宽度。

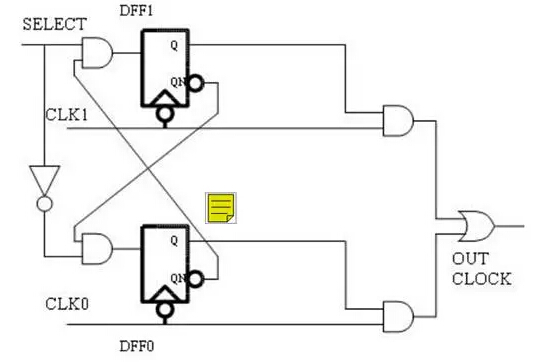

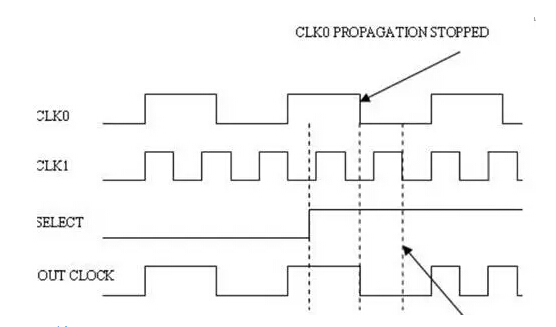

那么该如何消除毛刺,进而消除后面可能带来的问题呢,见下图,加入反馈电路。

反馈是为了确保时钟真正被关闭了,例如,select从0切换到1,也就是选择clk1,但是这时要确保clk0被完全关闭了,所以通过clk0时钟域的DFF反馈回来的1(如果能反馈1说明0已经进入到clk0时钟域的DFF中了)与clk1时钟域的select进行相与。

另外,为了解决跨时钟域的问题(select毕竟是不同于clk0,clk1时钟域的),通常还会加入1-2级的DFF。

另外,这几个电路使用时需要注意一点的是两个clk都必须要震荡起来后才可以进行select,否则进行切换可能导致select不能被正确的传送到的与门上,这样消除毛刺的功能可能就无效。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。