基于FPGA的2M误码测试仪设计

出处:shibiao145 发布于:2009-12-04 14:33:47

0 引言

无论是何种通信新业务的推出和运营,都离不开强力有效且高可靠的传输系统。随之而带来的问题就是如何对系统的传输质量进行测量和保证。

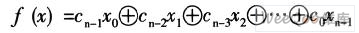

误码测试仪是一种能够测量和保证传输质量的智能化仪器,该仪器可通过检测来反映数据传输设备及其信道工作的误码损伤性能质量指标,并对其进行传输质量分析的有效工具。在电信运营、工程验收、科研、设备生产、教学实验等各方面,误码仪都是必不可少的通信测量和线路维护的辅助工具。目前在陕西省业务设备的接口应用中,百分之九十以上的接口是2M的接口,比如:交换网络上应用、信令网上的应用、数据网上的应用、网管网上的应用等,都使用了2M的数据。针对传统误码仪的不足,本文给出了基于Altera公司的cyclone系列FPGA芯片EP1C12-240PQFP的2M误码测试仪的设计方案。基于FP-GA的误码测试仪相对于传统的误码测试仪的优点在于其FPGA的内部逻辑功能是通过向内部静态存储器单元加载配置数据来实现的。其配置文件决定了逻辑单元的逻辑功能以及模块间或与I/O间的连接,并终决定了FPGA所实现的功能。FPGA的这种结构允许多次编程,并享有快速有效地对新设计进行优化的灵活性,故现今的通信系统大量采用FPGA作为系统的控制器件。本文重点介绍了FPGA内核中序列发生模块和序列接收模块中内容的设计。其中FPGA内核中m序列发生器的设计思想采用移位寄存器理论,并根据本原多项式来获得m序列移位寄存器的反馈逻辑式:

其中cn-1-i∈GF(2)是反馈系数,xi∈GF(2)是每位寄存器的状态。这样,结合cyclone系列FPGA芯片EP1C12-240PQFP的结构特点,就很容易实现反馈移位寄存器的逻辑功能。

1 误码测试系统的总体方案

误码一般是由通信系统中接收端抽样判决器的错误判断造成的,而造成错误判断的原因主要有两个:一是码间串扰,另一个是信道加性噪声的影响。误码测试仪存在两种设计方案,一种是误码仪的发射端模块和接收模块两部分独立,可用于单工的通信系统性能测试。但是由于该系统的测试序列需要动态生成,所以,其能够测试的系统码速只能和FPGA控制模块所能达到的速度相同。另一种方案是将发射端模块和接收模块结合在一个系统内部,这样能测试具有回环的通信系统,如双工通信的收发设备等。本文设计属于第二种方案,其误码测试系统框图如图1所示。图中,发送端模块产生的伪随机序列作为通信系统的信源数据流流经信道,接收端模块则接收来自信道输出的比特流,并将其与接收端模块产生的与发送端模块输出类型相同的伪随机序列进行比较,从而完成误码测试。误码仪由发送端的序列发生器1模快、接收端的位同步信号提取模块、帧同步码检测模块、序列发生器2模块、误码分析模块及外设接口构成。其中位同步信号提取模块的作用是获得位定时同步脉冲。帧同步码检测模块的作用是获取帧同步信号,以使两个序列能以同相位比较计算误码率。因为如果接收的测试序列与序列发生器2模块产生的序列两者相位不同,则误码的测试结果将毫无意义。

2 系统硬件设计

2.1 系统硬件组成

根据误码测试仪器的功能要求,在本系统的硬件总体架构中,将FPGA作为总控制器,并外扩E1接口模块,以用于实现码型和波形的转换,同时将FPGA输出的NRZ码型转换成适合于在E1信道中传输的HDB3码型,并将来自E1信道的HDB3码转换为NRZ码送入FPGA中;E2PROM存储模块则可将误码分析模块的误码测试结果进行存储,且掉电不丢失数据,并可随时读取,以便于在无人值守的情况下进行误码测试;LCM显示模块是为了使用户了解误码测试结果;RS232串口模块则用于和PC机通讯,上传误码检测结果,以便于从PC机上看到一段时间内误码率曲线图及其它误码信息,使用户了解通信系统的误码发生情况;此外,系统还外扩有键盘、电源管理模块、时钟电路、JTAG口和AS口。

2.2 E1接口电路的设计

E1的标准传输线路码通常采用三阶高密度双极性码(HDB3,high density bipolar),它是一种双极性归零码,是广泛用于PCM线路的传输码型。本文中的E1接口选用非平衡的75 Ω物理接口(一收一发)。E1接口芯片ET2154是一路E1PCM-30/ISDN-PRI收发器,它集成有时钟数据恢复及发送E1脉冲成型的片内线路接口单元(LIU)和E1帧处理器(Framer),其各项指标符合ITU-T的G.703、G.704、G.706、G.823建议等要求。ET2154的线路接口功能主要包括三部分。是接收器,用于处理时钟和数据恢复;第二是发送器,用于形成波形和驱动E1线路;第三是抖动抑制器。

(1)E1线路接收接口

当HDB3码流从E1线缆经BNC接口进入,并通过一个1:2的变压器耦合至RTIP租RRNG输入管脚后,其接收模块将允许用户设置寄存器以匹配外部线路的阻抗。ET2154中的数据时钟恢复模块可从HDB3码流中恢复时钟和数据。从HDB3码流中恢复出时钟和数据可通过高倍采样来实现,首先由外部提供一个2.048 MHz的时钟信号,然后由芯片内部PLL将它16倍频到32.768 MHz 。即先对每位HDB3码进行16倍的采样,然后由时钟恢复系统利用16倍的采样时钟来恢复时钟和数据。其E1信号接收示意图如图2所示。

正常情况下(RTIP,RRING有信号输入),在RCK(接收方向恢复时钟)管脚输出恢复后的时钟信号。而当ET2154被配置成输出NRZ数据模式时,则在RSER管脚输出恢复出的串行数据信号并送入FPGA。

(2)E1线路发送接口

待传输的串行数据流一般由XSER (发送串行数据NRZ)管脚进入ET2154,并在XCK(发送方向输入时钟)管脚接收来自FPGA的2.048 MHz的时钟信号。ET2154主要由内部精密的数模转换器(DAC)来产生要发送到E1线路上的波形,这种波形符合ITU G.703规范。系统中的发送器可将模拟波形从TYIP、TRING管脚通过1:1.36的升压变压器耦合到E1线路上。其E1信号发送示意图如图3所示。

(3) E1线路控制接口

ET2154的工作方式和特性是通过对其外部管脚的控制来实现的。通常将这些控制管脚连接至FPGA的外部I/O口,由FPGA来进行控制。ET2154与FPGA的连接电路如图4所示。ET2154通过内部寄存器的配置来设置其工作方式,FPGA则利用8位数据/地址复用线AD0~AD7来对ET2154内部的寄存器进行设置,从而实现所需要的功能。

3 系统软件设计

在对系统软件进行设计时,可将误码测试系统的功能分为各个功能模块,然后用VHDL语言编程实现FPGA芯片内部各个功能模块的硬件逻辑,整合完成设计。本误码测试系统的FP-GA内核中的功能模块有时钟分配模块、序列发送模块、序列接收模块、LCM控制模块、I2C控制模块、RC232串口控制模块、键盘消抖及扫描处理模块、总控制模块等。FPGA内核中各个模块之间的相互关系如图5所示。

3.1 键盘处理模块

本系统中的键盘处理模块包括按键的消抖和键盘的扫描处理。由于键盘模块的设计直接和用户的输入控制相关,用户的一切控制结果都和按键输入相对应,所以可将总控制模块和按键处理模块放在一起考虑。

3.2 时钟电路

时钟是整个系统设计中重要的一环。序列发送、序列接收、对E2PROM模块的读与写、串口通信的波特率以及LCD显示等都离不开时钟信号的控制,这就需要系统内有一个基准的时钟模块来提供所需要的时钟信号。时钟模块可由锁相环和分频器模块构成。通过对QuartusⅡ中mega-function模块ALTPLL的定制可生成PLL,inclk0是外部有源晶振提供给FPGA的clk0引脚的16 MHz时钟,可经过PLL产生C0、C1两个时钟信号,其中C0是inclk0的2倍,为32 MHz,可作为序列接收模块中对测试码进行采样的采样时钟。而C1是inclk0的3倍,为48 MHz,设计时可将C1信号送入分频电路获得2 MHz时钟,作为序列发生器的时钟;也可将C1信号经分频电路获得1 MHz时钟,作为I2C控制模块的读/写及键盘模块的时钟信号;当C1信号送入UART控制模块和LCM控制模块后,可通过各自模块内部的分频电路获得所需要的时钟。图6所示的PLL模块中方框内表格中的各项内容分别表示信号名称、信号倍率、信号相位及占空比。

3.3 测试序列发送模块的软件设计

测试序列采用m序列时,ITU建议用于数据传输设备测量误码的m序列的周期是511,其特征多项式(本原多项式)建议采用f(x)=x9+x5+1,本文应用移位寄存器理论从本原多项式出发来产生m序列,本原多项式是f(x)=x9+x5+1的m序列的VHDL语言编程如下:

在Ahera的Quaaus II开发平台下,本原多项式f(x)=x9+x5+1的m序列的仿真波形如图7所示。

3.5 帧同步信号检测

对帧同步电路的一项基本要求就是要迅速发现失步,以便及时恢复同步。若在发送端插入帧同步码“0011011”,那么,在误码检测时,由于E1串行数据流中也会出现“0011011”这样的内容,因而难以判断哪些是帧同步码,哪些是数据内容,所以,在设计中,可采用计数器来进行帧同步码的定位。E1的帧周期为125μs,两帧即为250 μs,这样,若规定当捕捉到个同步序列后,只有在一段时间内,每间隔250μs,可连续三次(计数器计数)捕捉到这个同步序列时,才认为找到了帧同步。与此类似,在一段时间内,如果连续三次都没有捕捉到帧同步序列,那么,即可认为帧同步丢失。其帧同步信号检测流程如图9所示。

在单个帧同步序列捕捉的FPGA实现中,“0011011”序列的捕捉由输入序列移位寄存器、相关运算阵列和相关求和网络等部分组合完成。工作时,帧同步码序列“0011O11”首先进入相关运算阵列,而输入数据流则在时钟驱动下被送入输入序列移位寄存器中。在相关运算阵列对输入序列和帧同步码进行相关运算后,可将结果送入求和网络。输入序列移位寄存器每更新一位数据,相关运算阵列就进行相关运算,而求和网络则对每次的结果都进行求和计算。求和网络输出的相关值需要与一个检测门限值作比较,以判断是否出现同步码。检测同步码“001 1011”的模块如图10所示,它由7个触发器、7个异或非门和一个8输入与非门构成。该电路可以检测出sequence串行输入的数据流中包含的特殊码字“0011011”,其中利用地线和电源线可将相关运算阵列的一个输入自右向左的连接成“0011011”,与同步码字对应的另一个输入端接输入序列移位寄存器的输出,7个对应位可进行异或非(同或)运算,对应位匹配时,结果为“1”。7个异或非门的运算结果进入求和网络后,只有当7位对应位全都匹配时,捕捉信号SYN才有效(有效状态为“0”),此时表明找到了同步序列码。

4 结束语

本文所介绍的误码测试系统采用以大规模现场可编程逻辑器件FPGA及外围接口芯片构成,文中详细介绍了系统硬件架构中EI接口电路以及FPGA内核中序列发生模块和序列接收模块中内容的设计方法,并给出了部分模块的仿真波形。整个误码测试系统仪器结构紧凑。实验表明,该系统在线检测的速度和稳定度方面都有大的提高。

参考文献:

[1]. RS232 datasheet https://www.dzsc.com/datasheet/RS232_585128.html.

[2]. BNC datasheet https://www.dzsc.com/datasheet/BNC_2319479.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PLC的34个基础知识2024/1/17 16:25:58

- 印刷电路板的组装方法2023/9/15 17:04:46

- 模拟量输入测量值显示满量程(上溢)的故障处理方法2023/8/31 11:09:13

- 什么是PLC?看完就明白2023/5/5 16:37:01

- 可编程逻辑控制器 (PLC) 中的梯形逻辑2023/4/23 15:48:34