一种数字存储示波器智能触发技术研究

出处:刘永征521 发布于:2010-12-23 16:26:49

摘要:针对测试者捕捉和观察混杂在周期信号中的偶发、异常信号的需求,提出了一种数字存储示波器的智能触发方法。首先分析了传统测试方法效率低、测量方法受限等弊端,然后介绍了智能触发技术的总体设计方案、工作流程和技术优势,其是通过硬件实时判别能任意设置的可编程触发模板,给出了将该技术实现于某型号数字存储示波器的具体实施方法以及应用验证结果。测试表明,该技术具有较高的偶发、异常事件捕获效率,是对示波器波形捕获功能的有益补充。

0 引言

在时域测试领域中,数字存储示波器的应用越来越广泛。其中,示波器对偶发、瞬态事件的捕获能力成为衡量其数据采集性能的一个重要指标。

为了解决这一问题,通常采取的措施有2种:一种是示波器的波形采集和显示采用并行处理架构,从而提高示波器单位时间内捕获并显示波形的幅数,即提高示波器的波形捕获率。

捕获率越高,示波器捕获到异常事件的概率越高。如美国泰克公司推出的数字荧光示波器,它是一种不仅能捕获和显示信号的时间- 幅度(事件)信息,而且能够以不同的辉度或颜色等级显示事件出现概率的数字存储示波器,其波形捕获率达300 000 wfms/ s;另一种方法是采用数字示波器的无限余辉功能,通过长时间的捕捉波形来发现异常或偶发事件。尽管通过这些方法都能够有可能发现这些偶发、瞬态信号,但总的来说效率都比较低,发现这些信号都需要较长的时间,且由于这两种方法都将多次触发采集的波形叠加在一起,对测试者来说很难正确的甄别和观察异常信号,给测试带来不便。

针对测试者捕捉和观察混杂在周期信号中的偶发、异常信号的需求,文中提出了一种数字存储示波器的智能触发方法,以便能更加自如的观察和分析故障信号产生的原因,从而提高用户的测试效率。

1 传统测试方法的效率分析

数字示波器捕获异常信号的量化方法可以通过示波器每s在屏幕上累计的异常事件的次数来表示。也可以转化为在屏幕上看到相邻两次异常事件的平均时间。

传统方法是采用具有较高波形捕获率的数字荧光示波器,触发方式采用边沿触发,观察叠加显示的波形,等待一段时间后期望能从三维累积的波形中观察到异常信号。

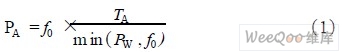

采取这种方法时,异常事件的捕获率与波形的频率、示波器的波形捕获率和异常事件发生的统计概率等相关。设示波器捕获某异常事件的概率为PA ,示波器的波形捕获率是PW ,异常事件出现的平均周期是TA ,被测周期信号的频率是f0 ,可以得到下面的关系式:

从式(1)中可以看出,如果波形的频率不超过示波器的波形捕获率,那么示波器能捕获每个触发事件,因此也就能捕获到每个异常事件;当波形的频率超过示波器的波形捕获率,示波器则不能捕获每个触发事件,每s捕获到异常事件的次数等于异常事件发生的周期乘以信号频率再除以示波器的波形捕获率。

例如,一个信号周期100 MHz的正弦信号,在该信号中平均每隔2 s出现1 次毛刺干扰, 采用波形捕获率为300 000wfms/ s的高性能数字存储示波器来观察,由式(1)可以计算出捕获到该毛刺信号的时间大约是667 s,可见捕获效率非常低。

由于数字存储示波器工作机制是采集、处理、显示3个步骤周而复始循环,在处理和显示这两个环节中示波器是停止采集信号的,这段时间称为示波器的“死区时间”。在死区时间内,示波器将漏失掉这段时间的大部分波形。不难发现波形捕获率和“死区时间”的关系是:波形捕获率越高,“死区时间”越小,那么采集波形的漏失率就越低,发现并捕获异常事件或瞬态信号的能力就越强。

对于这种传统的方法,当信号频率小于示波器的波形捕获率时能够保证在异常事件发生时捕获到信号,但一旦信号频率超过示波器的波形捕获率时,捕获的概率就下降了。因此大多数示波器设计了快速采集模式来弥补这一缺点。然而,为了实现这种采集模式却牺牲了数字示波器主要的分析和计算功能,尽管用高捕获率的示波器来观察信号,也只能起到观察叠加波形轨迹的作用,而且大部分正常和少部分异常信号全部叠加在一起显示,对测试者分析异常信号带来困难。

如果测试人员要测量和分析异常信号的特征,用现有的方法很难实现,且测试效率低下,为此文中设计了一种示波器的智能触发方法,类似任意波形发生器一样,用户可以通过任意的设置不同的触发模板,再将触发模板转换为硬件触发比较的条件,通过对被测信号进行实时监测,直至找到满足触发模板设置条件的那段信号后才产生1次触发,从而达到捕获异常信号的目的。

2 智能触发技术

2.1 总体方案

智能触发技术的总体方案如图1所示,主要由采集和样值存储模块、一般触发模块、可编程触发模块、触发选择与触发释抑模块、中央处理模块五大部分及与之相对应的处理软件组成。

图1 智能触发方案系统框图。

采集和样值存储模块主要由高速率8 bit模数转换器(ADC) 、高速率先进先出存储器( F IFO) 、采样控制模块并辅以相应的逻辑控制电路组成,负责完成模拟信号的采集和有效波形数据的存储功能。

一般触发模块的功能是完成传统数字存储示波器的大部分触发功能,即边沿触发、视频触发、脉宽触发、斜率触发等。

它的组成可以细分为触发电路、2个16 bit数模转换器(DAC) 、2个高速比较器、触发产生与合成模块四部分组成。触发电路实现对输入模拟触发信号的整形和电平变换; 2个模数转换器分别为高速比较器提供用户可以任意设置的触发比较电平,触发信号与比较器比较后的输出送入到触发产生和合成模块中;触发产生和合成模块根据用户所选择的触发方式进行计算和判别,送出满足要求的触发信号。

可编程触发模块是实现智能触发的。如图2,它包括n个8 bit的高速数字比较器、n个存储深度可由用户调节的触发模板存储区( SRAM) 、触发灵敏度控制器以及触发信号合成模块四部分组成。

触发选择与触发释抑模块由一个多路选择器和触发释抑控制器组成。多路选择器负责完成一般触发信号和可编程触发信号的选择;触发释抑是发生正确触发后的一段时间,在这段时间内,示波器不能触发。当触发源是复杂波形的时候,该特性能发挥作用,其结果是,只有在适当的触发点示波器才能触发。

图2 可编程触发模块原理框图。

中央处理模块主要由一片高性能的DSP处理器组成。它主要负责数据采集、触发控制、触发模板的编辑、其它触发参数的设定等工作。

上述模块大部分功能集成在一款高性能的可编程逻辑器件( FPGA)中,如图1中虚线框所示。

2.2 工作流程

其工作流程是先由用户设定触发模板存储区的大小n,然后在所设定的模板存储区内编辑触发模板并设定相应的触发灵敏度S及触发条件(大于、小于、等于和不等于) ,所设定的触发模板可以是单一触发模板,也可以是组合触发模板。组合触发模板的逻辑关系可以选择“逻辑与”、“逻辑或”、“逻辑异或”、“逻辑同或”等。

设定完毕后随即启动采集,采集到的原始数据送到高速数字比较器与触发模板存储区的个数据进行比较,如果满足触发灵敏度设定的条件则指向触发模板存储区的第二个数据,让第二个采样原始数据与其进行比较;如果不满足触发灵敏度设定条件,则仍然让第二个采样原始数据与个模板数据进行比较;以此类推,直到这段原始数据与触发模板存储区的所设定参数完全相符合时,才产生一个触发使能信号,该信号再送到触发信号合成模块中,结合用户设定的触发条件进行触发脉冲的合成。假设原始采样数据为X,触发模板存储区的数据为Vn ,触发灵敏度为S,触发条件为等于,则比较器的数学表达式如式(2)所示:

2.3 技术优点

该智能触发技术除了可以满足传统数字存储示波器的常用触发功能外,还提供了一种新颖的可编程触发模式,而且实现成本低廉,性价比很高。用户可以随心所欲的设定触发波形模板(模板可以通过人机界面在屏幕中编辑,也可以是示波器采集到的一段波形数据) ,还可以动态的调节触发灵敏度等指标;而且触发波形模板的深度可以根据触发模板的复杂程度在一定范围内调整,增强了触发设置的灵活性和可重构性,采用这种方法可以轻松地捕获较复杂波形。

触发信号产生的基本原理是在硬件中将原始数据与触发模板中的数据在一定灵敏度范围内进行逐一比对,所以对于传统的任何一种触发方式都可以通过触发模板的设置来实现,甚至还可以设置成等效于多种组合的触发方式。例如,用户可以在同一个触发模板中既设置一定条件的脉冲宽度,又设定一个定斜率的三角波,这就等效为在触发判别的过程中先进行脉宽触发,然后再进行斜率触发。另外,还可以采用多触发模板的方式,派生出更多、更复杂、更智能的触发判别方法。

3 应用验证

文中提出的智能触发方案和相关电路在某型号采样率为1GSPS,模拟带宽为100MHz的数字存储示波器产品中得到了实际应用。

3.1 具体实现

方案的实施可以分为模数转换与样值存储和触发。模数转换根据所设计数字存储示波器要达到的采样速率和分辨率来选择,这里选用4片AD I公司的250MSPS/8 bit的ADC并行采样来实现1GSPS采样率。样值存储也需根据存储深度指标的要求来选择,目前FPGA内部所集成的存储器容量已经达到Mbit量级,能够满足一般场合的应用,又因大部分触发功能都在FPGA中实现,故选用性价比较高的Xilinx公司Spartan 3A系列FPGA.

触发模块分为一般触发模块和可编程触发模块。一般触发模块包括触发电路、高速比较器、触发产生与合成模块,触发电路主要完成触发源的选择、触发信号的整形、视频触发信号的分离等功能,它是由一些分离元器件搭建而成;高速比较器选用AD I公司的超高速ECL比较器AD96687,它具有两个比较器,刚好满足本方案的要求;触发产生与合成模块是纯数字电路,可以在FPGA中实现。另外,可编程触发模块的实施也集成在FPGA中。它包括n个8bit的高速数字比较器、n个存储深度可由用户调节的触发模板存储区( SRAM) 、触发灵敏度控制器以及触发信号合成模块四部分组成。

由于需要用户编辑触发模板,故需提供较复杂的人机接口界面,再加上数字存储示波器对数据采集的实时性要求,中央处理器的性能就决定了整个系统的性能,因此选用高速、高性能的嵌入式处理器。

3.2 异常事件的捕获测试

该智能触发技术为用户快速查找并定位夹杂在周期信号中的异常信号提供了一种有效手段。

测试中只要获取了正常信号的特征,然后再将该信号的特征作为触发模板,使系统采集不满足触发模板的信号来实现异常信号的捕获,并且捕获到的信号还可做进一步的分析和处理。测试方法主要分为2个步骤。

(1)输入被测信号,设置触发方式为普通的边沿触发,然后开始采集,当采集稳定后停止,此时捕获到的信号应该是周期的正常信号,将此时采样得到的信号作为触发模板保存下来;(2)打开示波器的智能触发功能,并把上一步保存下来的触发模板信号导入,设置合适的触发灵敏度,设置触发条件为不等于,设置触发方式为单次触发,随后启动采集,此时由于绝大部分信号是正常信号,是不满足触发条件的波形,示波器的采集应长时间处在等待触发的状态中,直到异常信号发生时,示波器才完成采集并停止下来,这样屏幕上观察到的就是异常信号了。

图3给出了示波器捕获到的异常信号屏幕截图,输入信号是由任意波形发生器产生的5 MHz正弦信号,信号中每5 s叠加了1个周期性的窄脉冲信号,图中阴影部分是设置的触发模板示意图。

采用上述测试方法的智能触发技术,一旦异常信号发生,就可以立即捕获到此信号,提高了测试效率。

图3 采用智能触发捕获到的异常信号。

4 结束语

文中提出的智能触发技术为用户快速查找和分析夹杂在周期信号中的异常信号提供了有效手段,是对数字示波器快速采集功能的一种有益补充,用户可以先利用快速采集功能观察被测信号中是否有异常信号,然后再用智能触发功能来单独捕捉和进一步分析。目前该技术已申请并成功应用于某型号的数字存储示波器中。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 三坐标测量仪使用步骤及注意事项2024/4/11 17:54:47

- 如何提高接地电阻2024/4/11 16:38:47

- 电流互感器的操作、类型和极性注意事项2024/4/2 17:11:19

- 如何识别变压器引线2024/3/29 17:13:57

- 精确电流测量的模拟直流电流表知识2024/3/28 17:45:12