基于C8051F340的非易失大容量数据存储方案

出处:awey 发布于:2010-12-08 16:49:38

摘要:海洋仪器在后期数据分析处理时数据存储电路是不可或缺的。针对海洋仪器对数据存储大容量非易失的要求,结合实际工作经验,给出几种扩展海量存储器的方案和实际电路。这些方案是以C8051F340为主控制器,充分利用C8051F340片上集成的I2C,SPI和I/O接口资源扩展大容量存储器,相比于传统的存储电路,省去了译码和锁存电路,同时简化了软件编程。经实际应用,这些存储电路工作稳定、功耗低,适用于中低速,需存储大量数据的仪器仪表。

在海洋仪器工作过程中,观测的周期比较长,累积的数据量往往比较大,要求使用大容量存储器。而且由于海洋环境恶劣,很多时候电池耗尽,仪器尚未回收,为了保证数据安全,必须采用掉电非易失存储器。EEPROM和Flash闪存,既有ROM的特点非易失性,又有比较高的存取速度,而且易于擦除和重写,功耗很小,集成度高,是比较好的选择。但早期的存储电路通常比较复杂,因为其存储器容量小,接口单一,为了扩大容量需要外加扩展地址线的译码和锁存电路。随着电子技术的发展,各种大容量存储器层出不穷。这些存储器在内部结构、实现技术、物理外观和工作电压等方面有较大差异,而在硬件接口上常见为I2C接口、 SPI接口和并行接口。

以Microehip公司生产的C8051F340为主控器,提出基于多种硬件接口的大容量存储设计方案,可方便移植到与51兼容的其他单片机系统。

1 C8051F340特性及硬件接口

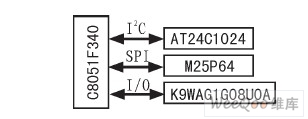

C8051F340是Sihcon公司生产的混合信号片上系统型单片机。它的内核具有标准8052所有外设,包括2个全双工UART、1个增强型SPI端口,1个SMBUS端口,40个I/O引脚,4 352字节的内部RAM,128字节特殊功能寄存器等。C8051F340片上丰富的硬件资源,使其方便扩展不同的接口存储器。图1是基于C8051F340的硬件接口(I2C,SPI,GPIO)实现的3种大容量存储器扩展方案的示意图。

图1 大容量存储器扩展方案

2 I2C总线扩展EEPROM存储器

2.1 I2C总线

在并行总线系统,CPU要完成与外部RAM或ROM的交换数据,通常需要有3组总线(地址、数据、控制总线),采用如此多的并行总线可使控制速度快,与存储器交换数据方法简单。但是,在绘制电路板时,这些总线将耗费很大空间。而I2C存储器克服了这个缺点,它仅需要数据线SDA和时钟线SDL 2条总线即可。数据交换速率要求在ms级的场合,I2C存储器可以取代并行存储器。

2.2 AT24C1024及与C8051F340的软硬件设计

AT24C1024是l Mb支持I2C数据传送协议的串行CMOS EEPROM,其内部结构为512页,每页为256字节,可用电擦除;它具有2种写入方式,一种是字节写入方式;另一种是页写入方式。允许在一个写周期内同时对1个字节到l页的若干字节的编程写入,l页的大小取决于片内页寄存器的大小。AT24C1024具有256字节数据的页面写能力。

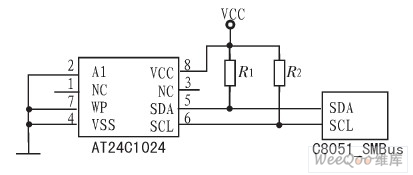

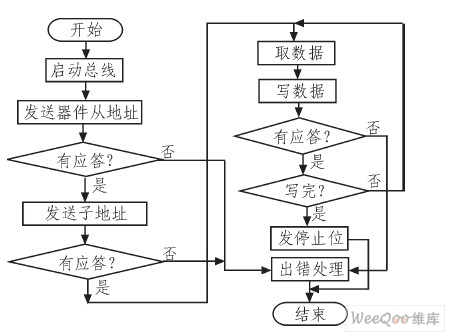

C8051F340片上集成SMBus端口。SMBus完全符合系统管理总线规范1.1版,并与I2C串行总线兼容。连接在I2C总线上的器件,SCL和 SDA应该为漏极开路或集电极开路输出,当总线空闲时,这2条线都被拉到高电平。所以,在配置C8051F340端口时,把SDA、SCL配置为漏极开路输出。为了使开漏极电路输出“l”时SDA和SCL应是高电平而不是高阻态,这就需要加上拉电阻。图2为AT24C1024与C805lF340的硬件连接图。对AT24C1024的操作编程,与一般I2C类似,遵循I2C通信协议。以写操作为例,其流程图如图3所示。读操作与此类似。

图2 AT24C1024与C805lF340的硬件连接图

图3 流程图

2.3 应用举例

此电路用于小型的海洋温度计,在采样率为1/6 Hz、采样16位的情况下,可连续存储109 h左右。小型温度计以体积小,重量轻等特点使其方便在海上进行多点多深度布设,用于测试水下温度场的一天连续变化。但是AT24C1024存取速率较低,仅适合于低速存取的场合。在某些系统中还用于存储系统配置参数和保存系统工作日志。

3 SHI接口扩展M25P64

3.1 SPI总线

串行外围接口SPI总线可分为3线和4线工作方式,支持在同一总线上挂接多个主器件和从器件。SPI收发独立,可同步进行,通信速率比较高。

3.2 M25P64及与C8051F340的软硬件设计

M25P64是低功耗、大容量串行Flash存储器其存储空间为64 MB,由32 768个页面组成,每个页面为256字节。支持页编程(256字节),扇区擦除(512 KB)和块擦除(64MB)。时钟频率50 MHz;可循环使用100 000次;保存数据年限超过20年;该存储器工作于3/4线串行总线方式,可扩展更大容量的存储空间。

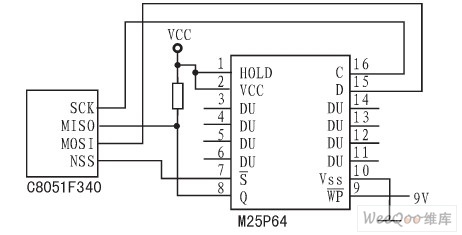

对M25P32的读写可以直接将M25P64与C8051F340的GPIO口连接,采用GPIO口模拟SPI接口时序的方法。使用C8051F340的片上SPI控制接口,将引脚C与单片机输出时钟对接,数据输出Q与MISO对接,数据输入D与MOSI对接,片选信号 与NSS对接,如图4所示。

与NSS对接,如图4所示。

图4 M25P64与C8051F340的GPIO口连接

C805lF340上电后首先对硬件接口进行初始化,把端口设置为SPI特殊功能。C8051F340通过读写SPI数据寄存器(SPIDATO)实现在 SPI通信线上的数据收发。因此,对M25P64的读写和擦除可归结为,按照M25P64数据资料上的命令表,往SPIDAT0里写入命令和数据,程序流程的控制

通过判断从SPIDAT0读出的状态寄存器位。

3.3 应用实例

此存储电路中M25P64占用的I/O口线较少。M25P64相比于AT24C1024附加了片选信号,并且数据输入和输出线分开,使存储电路的抗干扰性有所提高,降低了软件设计难度。M25P64在硬件实现上基于移位寄存器,所以通信速率较高,达到微秒级。此存储电路已成功应用于开发的湍流观测仪器样机。

4 GPIO口扩展K9WAG08UOA

C8051F340上未被交叉开关分配的端口引脚和未被模拟外设使用的端口引脚都可以作为通用I/O。在设计C8051F340,若不把选定的引脚配置为特殊功能,它就默认为通用I/O,利用这些引脚来扩展K9WAG08UOA。

4.1 K9WAG08UOA的特性

K9WAG08UOA是NAND-Flash架构的Flash,单电源2.70~3.60 V供电,内部存储空间为(1 G+32 M)x8 B,数据寄存器为(2 K+64)x8 B,可进行任意字节单元的读操作(长25μs),(128 K+4 K)B的块擦除和(2 K+64)B的页编程(200μs典型时间)。容量上可堪比一般的SD卡和U盘,读写速度也很快。

4.2 K9WAG08UOA与C8051F340的硬件连接

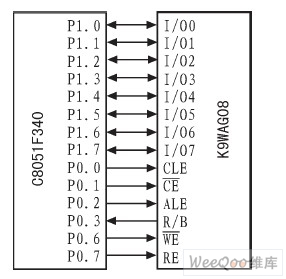

C8051F340与K9WAG08UOA的连接方法如图5所示。K9WAG08UOA的命令、数据、地址均通过8根I/O线传输,31位地址分5次写入地址寄存器,其内部译码确定块号、块内页号、页内字节号后寻址相应的单元,比相同容量的并行存储器节省了23根地址线。地址线的减少简化了电路设计,同时也提高了编程的复杂程度。指令、地址从I/O写入时,把 拉低,配合CLE和ALE信号线实现I/O口上指令和地址复用。

拉低,配合CLE和ALE信号线实现I/O口上指令和地址复用。

图5 C8051F340与K9WAG08UOA的连接图

4.3 软件编程

K9WAG08UOA的编程比通常的串、并行存储器复杂。实际应用中将页编程子程序、块擦除子程序、读操作字程序编写成子程序,在需要时进行调用。由图5 看出,C8051F340对K9WAG08UOA的读写操作均通过通用I/O进行。C805lF340对I/O端口的操作通过访问对应的端口数据寄存器。向端口写入时,数据被锁存到端口数据寄存器中,以保持引脚上的输出数据值不变;读端口数据寄存器将返回端口输入引脚的逻辑状态。具体举例来说,比如P0=0x80,表示Ox80被锁存到端口数据寄存器中,把CE引脚拉低,引脚产生一个上升沿,数据就被写入K9WAG 08UOA中的数据/命令寄存器。Ox8O为命令还是数据取决于CLE和ALE的状态,CLE为高,ALE为低,表示Ox80为命令字段;CLE为低,ALE为高,表示Ox80为数据。下面对K9WAG08UOA的页编程、页读、块擦除做详细的说明。

4.3.1 页编程

K9WAG08UOA的页编程是以页为单位的,它允许在一个页编程周期里写入1~2 112字节的数据。数据被加载到数据寄存器,然后调用内部写入过程写入正确的单元。在写入之前必须擦除,否则出错。页编程的步骤为:1)写入串行输入指令0x80;2)分5次写入编程首地址;3)写人数据,多2 112字节;4)写入页编程指令0x1O。启动内部编程操作。为了反馈写入操作是否成功,K9WAG08UOA的内部状态寄存器记录了写入状态,通过查询寄存器状态位O,判断写入是否成功。

4.3.2 页读操作

K9WAG08UOA读页面的操作过程为写入0x00到命令寄存器,然后输入5个字节的地址,再写入命令Ox30启动页读操作。选中页面的2 112个字节的数据不是立即输出到I/0口,而先被复制到K9WAG08UOA的数据寄存器。通过检测R/B引脚状态来判断复制操作是否完成。一旦R/B 为高电平后,表示复制完成。微处理器器控制RE不断的高低变化,数据寄存器中的数据将按照在芯片中的地址排列依次锁存输出到I/O口,此时读取I/O口电平即可。

4.3.3 块擦除

K9WACO8UOA的擦除操作以块为单位进行。首先写入擦除指令Ox60,然后分3次写入行地址。载入行地址后执行擦除确认指令0xd0来初始化内部擦除操作。通过状态引脚R/B了解擦除的进度,R/B为高电平表示内部擦除完成。通过检测状态位(I/O0)来检查擦除操作是否发生错误。

4.4 应用举例

本设计的单片机P1口与K9WAGO8UOA直接连接,其他控制引脚与PO口的引脚连接。为防止存储器误操作,在单片机复位后要进行初始化设置。 K9WAGO8UOA的优点是容量大,低功耗。海洋潜标在水下工作的时间通常为3个月以上,累计的数据量通常上百兆,K9WAG08UOA能够胜

任这样的容量要求。在实验室水池进行多次长时间测试,K9WAG08UOA记录的数据可靠。

5 结束语

利用C805lF340丰富的接口资源,可以方便地扩展大容量的存储器。本文介绍的3种存储器扩展方案采用不同的硬件连接方式,但都具有非易失、低功耗的特点,又各有特点,可以根据系统开发的具体需求,进行选择使用。通过实践,总结以下经验:1)提高系统存取效率,加入FIFO缓存。数据按时间顺序写入 FIFO,大到一定容量后再由处理器以块形式读出。这样可以避免MCU频繁进入中断,提高处理器的工作效率。2)在控制印刷电路板面积及布线复杂度上,使用I2C接口为简洁,SPI接口次之。3)读写速度上,并口Flash快,适应于微秒级存取;SPI接口次之,提高时钟频率也可达到微秒级;I2C接口慢,适合毫秒级的访问。4)容量上,NAND架构闪存(K9WAG08UOA)的存储单元采用串行结构,一页包含若干字节,若干页组成储存块,这种结构的优点是使得容量可以做得很大。因此,在容量和存储密度上,NAND闪存比其他结构的存储器大。仅从容量考虑时,优先选择NAND架构的闪存。

参考文献:

[1]. C8051F340 datasheet https://www.dzsc.com/datasheet/C8051F340_1389885.html.

[2]. M25P64 datasheet https://www.dzsc.com/datasheet/M25P64_1118062.html.

[3]. M25P32 datasheet https://www.dzsc.com/datasheet/M25P32_846542.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- cps是什么意思?cps的含义_cps的特征2024/4/16 17:56:11

- 你所知道的DCS系统都有哪些?2024/4/16 17:50:53

- 煤矿人员定位系统的功能及重要性分析2024/4/16 17:43:54

- 什么是冗余?2024/4/15 17:33:02

- linuxfind命令详解2024/4/15 17:27:22