BGA芯片级封装老化测试插座的设计研究

出处:LPC900 发布于:2011-10-25 14:47:23

摘要:由球栅阵列转向细节距BGA的行动正在受到降低封装尺寸要求的推动。此外,与增加功能有关的I/O数量的增加对降低阵列的间距进一步产生了压力。BGA封装在给定的面积当中将I/O的数量提高至化,对越来越小脚迹的需求推动了节距小于1.0mm封装的发展。近三年芯片级封装的发展是对更小封装的兴趣和需求的证言。为实现本项技术商品化所需支持的"基础设施",经常就是电路板接受任何新型封装的入门项目。该基础设施的重要元件就是老化测试插座。

细节距BGA封装含有的节距小于1.0 mm,对印制线路板工业和老化插座设计师们提出了许多挑战。如何使得接触焊球温度在125°C而不在接触焊球的底部或在焊球上留下明显的见证印记,是一个特别困难的问题。在焊球可用的空间中,为插座设计和生产出零件以接触和保持封装增加了这个问题的难度。本文将描述目前对接触焊球所采用的某些方法,以及采用节距在1.0 mm和0.75mm之间的双臂夹捏接触件的解决方案,并用它来说明如何克服这些挑战。

今天,有些闪存器件的封装采用0.65 mm节距,DSP具有100多个I/O,采用0.5 mm的细节距球栅阵列(FP–BGA)封装。对这些器件必须研制具有成本效益的老化插座解决方案。本文将对某些概念设计进行讨论,并对Sensata 公司的产品进行了分析。

引言

发明晶体管和集成电路的挑战一直是将更多能量和功能投入到更小的封装当中,同时使得封装便于处理和与外界对接。这样就造成了一系列按字母排列的封装,包括:DIP(双列直插式封装)、PGA(针栅阵列)、PLCC(无引线芯片载体)、LCCC(无引线陶瓷芯片载体)、QFP(四边引线扁平封装)、TQFP(薄形四边引线扁平封装)和BGA(球栅阵列)等。

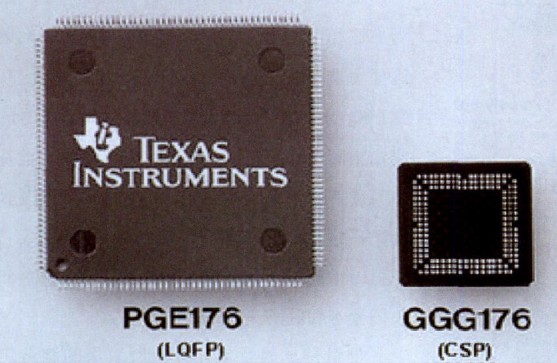

图1 CSP相对QFP的尺寸优势

个人电子工业的增长尤其在日本,为降低系统尺寸和重量提供了动机,成就了愈来愈小封装的发展。所有的封装路线图都指向裸芯片,然而,处理和试验的困难和成本已经推迟了裸芯片这一格式的广泛接受。作为常规封装和裸芯片近尺寸缩小攻关的妥协结果,已经研制出了尺寸大约为硅芯片尺寸的一类封装,即所谓的芯片尺寸或芯片级封装(CSP)。图1比较了作为QFP和作为FP–BGA而封装的产品尺寸的照片。英特尔公司表示,把8Mbit的闪存封装为?BGA时较与之相当的TSOP可减小尺寸达80%.

芯片级封装的接受和使用似乎在日本非常流行。虽然有50多种不同的CSP结构,半导体公司似乎都有他们自己的品种,处理和测试这些器件的困难已经向服务后端和测试基础设施的供应商发出了挑战。如果Gil Olachea的预言是正确的,这将继续成为令人关心的问题。按关于芯片密度增加的摩尔定律,Olachea已经提出:"半导体封装的数量每六年将近翻番。"这暗示到2010年,将有120种不同形式的CSP.

看好的一类CSP是FP-BGA.这是BGA的逻辑发展,节距和球体尺寸减小了。FP–BGA一般归类为BGA,其在中心的焊球小于1.0 mm,已写成或正在编写的节距标准为0.8、0.75 和0.5 mm.

设计考虑

一般商业问题

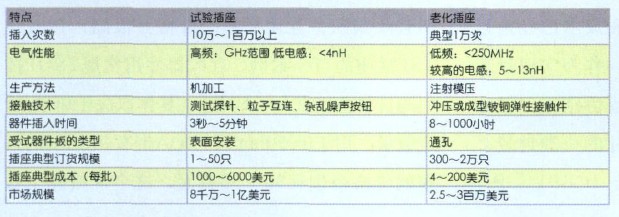

对老化插座的要求涉及对机械、电、热、可靠性和可重用性的功能考虑及商业成本问题。这些要求与试验插座的要求稍微有所区别。在不到1.00 mm节距上接触I/O的挑战对两种型号的插座均相同,然而,试验频率、重复使用次数及高温暴露有非常大的不同。Pfaff曾提供了涉及到研制CSP插座的商业和技术问题的极好述评。表1来自Pfaff的论文,总结了试验和老化插座之间的关键要求和区别。

表1 试验和老化插座要求比较

批量是试验及老化插座所采用的制造工艺和价格差别的关键。在一种新型封装的早期使用和验收期间,老化插座的价格会很高,这就是CSP插座的当今。存贮器件用常规TSOP插座的价格范围在6~15美元,具体取决于I/O的特定数量。用于0.75 mm FP–BGA带有48个I/O的插座的价格范围在35~50美元,这个价格完全按批量的大小来决定。供应商已经表示,该价格将遵循常规的学习/批量坡度曲线,当批量增加时,预计10~15美元的价格将是常见的。

人们对于CSP的各个性质和整体封装外形缺乏标准已经表示了关心。对这个问题尚不明确的是CSP插座是否将保持定制解决方案,实现降低成本的机会是,能够生产出销售到许多顾客的插座。关于这种设计的考虑将在下面说明。

据报导,CSP的市场在2008年大约为4亿只,在2010年为21亿只,CAGR达15%.其它预测没有如此有进取心,但是也表现了明显的增长机会,2010年CSP的容量在10~20亿只之间。虽然不是所有的封装都需老化插座,这一增长提供了实实在在的机会,插座供应商们正在辛勤地工作,以研制出具有成本效益的解决方案。

机械性能

在研制老化插座的过程中必须考虑几个设计问题,评述如下:

1.器件加载

基本上有两种类型的插座设计:蛤壳式和开顶式。蛤壳式设计对小批量手工加载和卸载看好。对于大批量的应用,优选零插入力或开顶式设计,这是因为采用目前的自动化设备,器件的加载和卸载简单易行。

图2是开顶式插座的照片,它设计用于54脚I/O的?BGA存贮器产品。图中示出了该适配器的轮廓,由适配器确定器件的位置,锁片使封装对准。

当按下插座的盖子时,接触件打开,锁片移动到侧面。将封装推入插座中,与适配器的侧边对齐。当把盖子闭合时,锁片引导封装并确保封装正确定位,使得接触件接住焊球。

2.插入次数

要求插座可以重复使用多次,典型的设计要求可插入1万次或2万次。这就对插座耐磨和耐应力的能力及弹性元件的低循环疲劳强度提出了要求。这些问题当中有许多可以运用有限元方法及快速原型测试方法在设计阶段进行评价,以便在投入硬模之前就测试基本设计。

3.接触焊球

这是一个复杂的问题,已经提出了许多不同的概念。设计问题包括:

A. 接触焊球而不造成任何损伤

B. 穿透表面氧化层

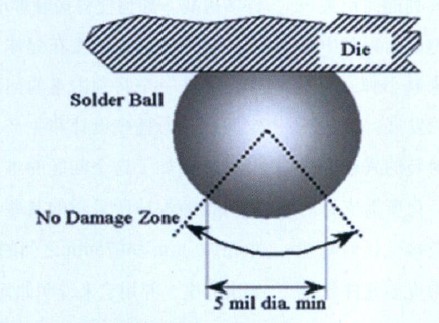

C. 如图3所示,保护NDZ(无损区)

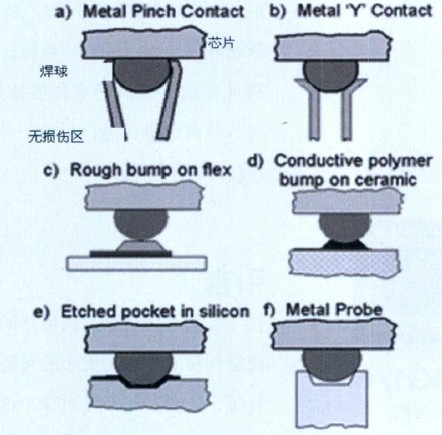

对于接触焊球,已经提出了若干种方法,分成三种基本类别。其中一些并不满足不触及焊球底部的要求:

A. 夹捏式接触件,运用某种弹性元件接触球的侧面

B. 探针接触件,例如测试探针和模糊按钮

C. 薄膜接触件,包括陶瓷体导电环氧树脂、柔体粗凸点和硅体袋状蚀刻

其中一些接触件示意于图4.为了更加全面的列举和说明,读者可查阅Crowley给出的CSP市场和技术分析。

4. 高温暴露

老化炉工作于各种不同的温度下。然而,典型的老化温度为150°C,在插座的寿命期间,在高温下的总时间可能超过1000小时。由于老化期间加载了接触件,弹性元件经过了应力松弛。其中一种弹性合金为CDA- 172000,它是一种铍青铜合金。这种材料由于其兼具有可成型性、模量大、屈服强度高和应力松驰性能好,已经广泛用于老化插座。

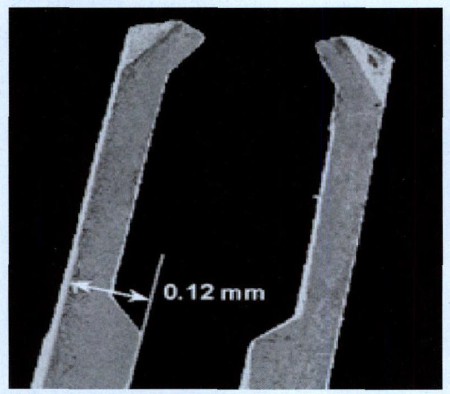

一种冲压成型的接触件由铍青铜制成,用于0.75 mm节距的插座示于图5.这是一种具备现代工艺水平的金属成型的零件,片状材料的厚度仅为0.12 mm (0.0047")。

夹捏式接触件的优点是:接触荷载是由应力悬臂梁簧片提供的,没有荷载施加于封装的表面。芯片上仅有的垂直荷载是通过使封装与插座对齐的锁片提供的。对于使用测试插针的接触件,电镀的凹点或其它种类的探针式插针必须经过芯片才能施加垂直荷载。既然在许多CSP当中,芯片就是封装,这意味着直接按压硅片,从而有可能损伤芯片。

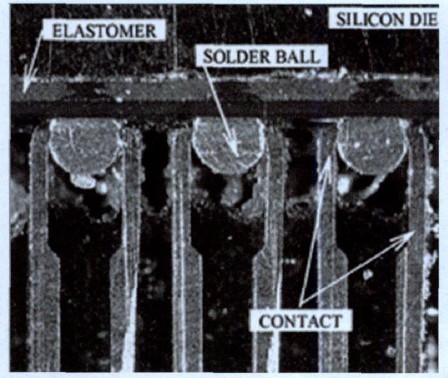

通过适当的设计和组装技术,夹捏式接触件可以满足要求,而不会在焊球的底部留下探针印记。图6是图3所示插座的横截面,芯片已就位,显示了许多接触件紧握焊球。接触点高于焊球的中纬线,接触探针标记处于"无损伤区"之外。这一夹捏动作具有试验期间将封装保持在插座中的好处。在经过125°C、9小时之后在焊球上留下的见证标记示于图7.

图6 插座的横截面显示接触焊球的夹捏式接触件

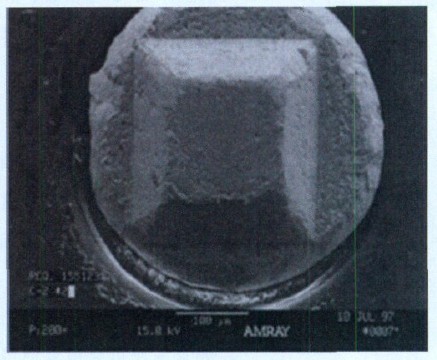

图7 在经过125°C 、9小时的老化之后,在焊球上留下的探针标志SEM照片

与BIB(老化板)的接口

大多数的老化板为通孔,标准印制板技术很容易接纳具有1.2~1.00 mm节距的插座。然而,对CSP,该节距小于1.0 mm,对高I/O数的器件,这会为BIB(老化板)制造商产生信号逃逸的问题,为I/O节距为0.75 mm的插座打出通孔并非常规方法所能,今天代价更加高昂。

为降低或消除与BIB接口的问题,可以使用一个内插器(适配器)。它也被称为扇出板,是一种焊接到插座底部上的小子卡。这个适配器以较为常规的1.27 mm节距向老化板提供了接口。此外,增加了插针的尺寸,提供了更大的强度且便于在BIB上装配操作。

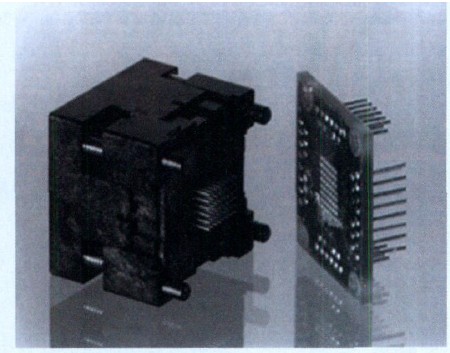

图8示出了一种内插器和插座。相比插座上的接触件尾体,内插器上插针的坚固性可见一般。内插器的脚迹大小与插座相同,因此,在BIB基板面中没有采用内插器的不利后果。插座的高度增加不到2mm (0.080")。

图8 用于48个I/0的0.75 mm CSP插座的内插器照片,用来使得与BIB相接更加方便

封装尺寸的变化

供应商的重大挑战将是在产品寿命期间适应封装尺寸变化的能力。芯片收缩是在半导体产品寿命期间降低成本计划的组成部分,对于常规封装的元器件,器件脚迹是在计划的开始就规定好了,芯片的收缩包括在封装之内,对于插座或其它试验接触器件没有影响。对许多芯片级封装来说,芯片尺寸规定了器件脚迹。随着芯片的收缩,整个封装的尺寸将减小,相当于一个新的封装或器件,就位的插座将无法在不经修改的情况下处理新封装。假定产品寿命期间某些芯片经历2或3次芯片收缩,这对基础设施成本的潜在影响意义重大。

图9 为在0.5 mm节距上接触焊球而蚀刻成的硅袋SEM照片

图10采用硅袋内插器老化后焊球的SEM照片

Sensata的插座设计师已经考虑到这一点,在图3中所示的插座有一个可移去的适配器。这个适配器是一种精密模压的零件,它使芯片与夹捏接触件对齐,甚至在把插座安装在老化板之后还可除去。这种通过替换适配器实现现场修整的能力,允许终用户方便地在元件寿命期间接纳封装脚迹中的任何变化。该适配器亦允许在许多场合中使用同样的插座,只要I/O脚迹相同,封装适合于插座的外形性能。

未来

对节距小于0.75 mm的封装具有成本效益解决方案的需求,已经被许多用户指明。今天人们可利用许多技术,但是认为它们不具有成本效益,并且不容易改装用于大批量处理和加工设备中的装机基础之中。总之,这些技术是为测试裸芯片而研制的载体的延伸。

在柔性薄膜上的接触焊盘

Sensata的DieMate产品具有MMS(大量生产系统)法生产的柔性薄膜,目前这一技术正在进行CSP使用评价。

导电环氧凸点

在陶瓷或柔体上的导电环氧凸点可以用来接触焊球。焊球的底部变形位于"无变形区"之内,具体依赖于所采用的接触荷载和温度/时间。

硅内插器

已经建议采用的另一方法是采用蚀刻而成的硅袋,示于图9.这是已知好芯片载体技术的另一延伸,造成的探针标志示于图10.可见焊球底部已经变形。

总结

今天,商业上已可为节距为0.8mm和0.75mm的芯片级器件提供老化插座。由于早期实施这种封装相关的插座批量较小,插座的价格高于用于常规封装的插座。这与CSP产品寿命周期的早期阶段相关,预测是价格将随着批量要求接近于与常规封装相关的批量而有所降低。已可供应用于0.5 mm节距封装的插座,然而,人们认为100美元的价格还是太高。据报导,许多公司正在研究设计问题,然而,低成本解决方案已经证明难以捉摸。随着消费产品的力量增加,对具有成本效益的0.5 mm插座的需求将推动研制工作。这里已经叙述了正在考虑之中的某些接触0.5 mm FP–BGA的方法。然而,还没有清楚地指明谁是赢家。

上一篇:压电传感器的信号调节

下一篇:漏电保护器测试系统的设计

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 三坐标测量仪使用步骤及注意事项2024/4/11 17:54:47

- 如何提高接地电阻2024/4/11 16:38:47

- 电流互感器的操作、类型和极性注意事项2024/4/2 17:11:19

- 如何识别变压器引线2024/3/29 17:13:57

- 精确电流测量的模拟直流电流表知识2024/3/28 17:45:12