基于FPGA的数字存储示波器的显示技术

出处:李涛 发布于:2011-12-05 10:24:31

摘要:本支主要讨论了一种关于FPGA+LCD的显示控制技术。该技术通过直接用FPGA产生LCD所需的显示控制时序来控制数据的传输和显示,与传统的采用专用芯片的显示技术相比,它提高了CPU的工作效率,简化了数据采集系统的结构,降低了成本。该技术已被成功地用于100 MHz的数字存储示波器中。

关键词:数字存储示波器,FPGA,LCD,显示

1 引言

由于液晶显示器(LCD)功耗低,体积小,超薄,重量轻,而且车身没有画面几何图形的失真及收敛性误差,也就投有了传统显示器中心和边角出现色差和失真的问题,因而得到广泛的运用。现场可编程门阵列(FP—GA)芯片具有高密度、小型化、低功耗和设计灵括方便等优点,可以缩短研发周期,提高工作效率,因而在数字电路设计中得到了广泛的应用。作为人机交互的LCD在数字存储示波器中有着重要的位置。在以往的设计中多采用液晶显示专用芯片去驱动LCD.宴践中发现它不但占用CPU资源,而且它与LCD数据接口之间存在干扰。为了解决这些问题.本文提出了.一种新的显示技术。

2 总体设计方案

由于数字存储示渡器对显示的实时性和刷新率都要求较高,而且它显示的大多是一些简单的图形和波形,因而直接用FPGA产生LCD所需的显示控制时序。存放显示数据的SRAM地址也直接由FPGA地址计数器产生。其显示系统总体框图如图1所示。

在图1中,A/U采集的数据经DSP处理,转换为LCD可以显示的点阵数据后再存储到RAM中}两片显示存储器RAMl和RAM2交替读取RAM中的数据,送到I。CD上显示。在FPC-A中设计了LCD显示时钟电路模块和显示数据传输电路模块。显示时钟电路产生LCD显示所需的各种时序;显示数据传输电路设计两路数据传输通道,RAM中的数据通过数据传输通道送到RAM1或RAM2中,再由LCD读取RAMl或RAM2中的数据显示。

对LCD及显示存储RAM的控制都由FPGA完成。

3 数据通道控制及实现

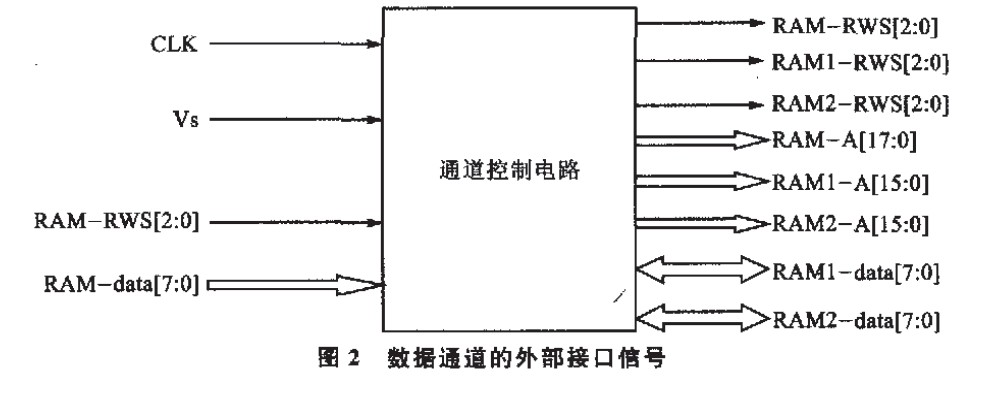

数据通道对存储RAM的读/写操作进行控制,保证数据正确地从RAM传送到RAMl或RAM2中,并能在LCD上正确地显示。图2为数据通道的外部接口信号。

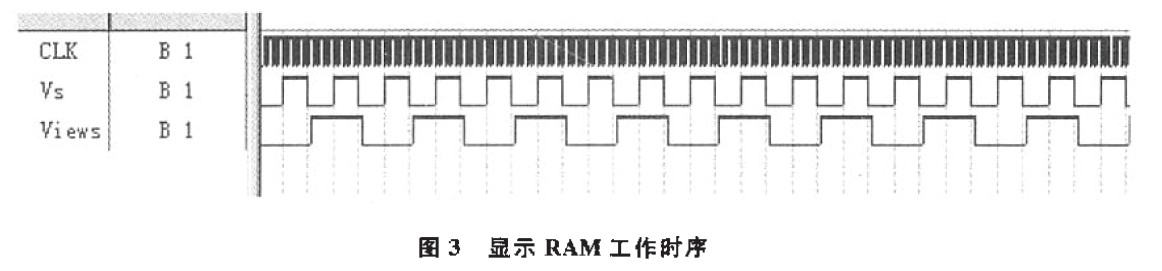

图2中,CLK为系统时钟,Vs为DSP提供的时钟;RAM—RWS[2:0]、RAM1一RWS[2 : 0]和RAM2一RWS[2:0]分别为RAM、RAMl和RAM2的读/写及片选信号;RAM—data[7:0]、RAMl一data[7:0]和RAM2一data[7 :0]分别为RAM、RAMl和RAM2的数据总线RAM—A[1 7:o]、RAMl一A[15:03和RAM2一All5:03为数据总线。由于采用了两片RAM作为显示存储器,它们可依次向液晶提供显示数据,这样,对每片显示RAM的读操作和写操作分开,避免了因为数据的改写而导致显示的小稳定。图3为显示RAM的工作时序图,图中Views为Vs反相后经二分频得到。

图3显示RAM工作时序

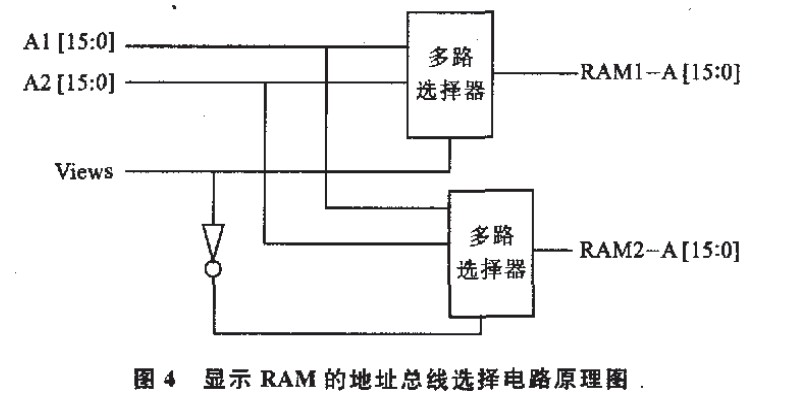

圈4显示RAM的地址总线选择电路原理圈数字存储示渡器的显示包括两部分:一部分是界面显示,包括菜单和光标的显示等;另一部分是波形显示。

波形是随时在更新,而菜单只有在按键操作的情况下才会改变,更新的次数很少。所以采用了分页显示技术,即将显示存储空问分成两个区间:一个区间用来存储菜单、光标等不常刷新的数据;另一个区间用来存储波形数据。每个区间都是一屏显示所需的空间。LCD显示时将两个存储区间里对应地址的数据通过FPGA内建电路相“或”以后再送LCD箍示。这样在软件处理时节省了重复刷屏的时间,同时简化了软件的编写。

4 显示时序电路设计

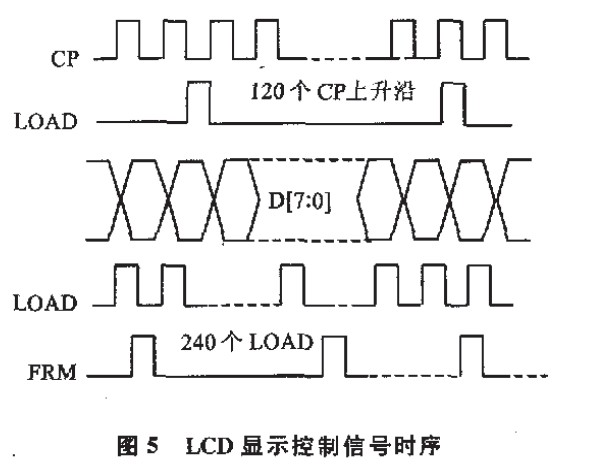

彩色液晶显示器(采用NANYA公司的LCBFBLB61V4)有3根控制信号:CP、LOAD和FRM信号。其中,CP为移位脉冲信号,每来一个移位脉冲信号,LCD就从数据线上读取显示数据。LOAD为行装载信号,当LeD读取一行数据后,会产生一个LOAD信号,将数据锁存起来。FP,M为场同步信号.每显示一屏数据就会产生一个FRM信号。彩色液晶的每个像素点的显示状态由3位数据的逻辑电平表示,因此显示一行需320×3/8=120个cP时钟,而3根信号线之间的关系为:LOAD的频率是cP的120分频,FRM的频率是LOAD的240分频。I.CD要求的显示控制时序如图5所示。

图5中各显示控制信号在FPGA中通过分频器实现:100 MHz系统时钟32分频得到3.125 MHz的移位图4为显示RAM的地址总线选择电路原理图。图中A1[15:0]为LCD显示RAM的读地址,A2[15:0]为显示RAM的写地址,它们分别由硬件时钟产生的地址计数器的输出线。Views为多路选择器的选择信号,其工作原理为:当Vs为低电平时,DSP占用RAM总线,RAM的地址总线由DSP的地址总线产生,DSP把处理后的数据送到RAM中;当Vs为高电平时RAM自动执行读操作,其读地址在FPGA中由硬件时钟地址计数器产生,即自动把RAM中的数据送到RAMl或RAM2中;当Views为高电平时,RAM中的数据送到RAMl中,此时RAM2中的数据送到LCD中击显示,当VJews为低电平对,RAM中的数据送虱RAM2中,此时RAMl中的数据送到LCD中去显示。当然在FPGA设计中还应包括存储器的读/写、片选电路和地址译码电路等,这里不再详述。

脉冲信号CP,再将CP信号120分频得到行装载信号LOAD.将LOAD进行240分频得场同步信号FRM。

5 结束语

本文所介绍的示波器显示技术已成功地运用于100 MHz数字存储示波器中。该设计能高效、可靠地实现数据的传输及波形的重现,提高了系统的抗干扰能力,降低了成本;并且该结构具有很好的可移植性,只须做很少的改动就可应用于不同的系统中。

参考文献:

[1]. All5 datasheet https://www.dzsc.com/datasheet/All5_2058595.html.

上一篇:全分辨率自由立体显示技术

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 分布式光伏发电的工作原理、特点及优势2024/4/23 17:53:20

- 一文详解发光二极管2024/4/22 17:31:28

- 一文详解发光二极管LED2024/4/10 17:57:25

- 安装FFC柔性连接线2024/4/2 17:02:42

- LED驱动电路的工作原理2024/3/21 16:41:50