基于FPGA的高性能DAC芯片测试与研究

出处:awey 发布于:2011-03-23 09:08:48

D/A 转换器作为连接数字系统与模拟系统的桥梁,不仅要求快速、灵敏,而且线性误差、信噪比和增益误差等也要满足系统的要求[1]。因此,研究DAC 芯片的测试方法,对高速、高分辨率DAC 芯片的研发具有十分重要的意义。

目前,波形测量和分析协会已提出了DAC 测试的技术标准IEEE Std.1057,里面的术语和测试方法为DAC 测试提供了更多的参考。传统的标准测试只适于信号发生器、示波器等测试仪器,但是测试不高;大规模芯片测试时则使用自动测试设备(ATE),但是成本很高;近提出的DAC 的测试方法,比如结合V777 数字测试系统可以进行DAC 测试,应用模拟滤波器进行音频DAC 测试,利用数模混合信号测试系统Quartet 对高速DAC 进行测试,等等[5],这些方法在通用性、度和成本方面无法同时满足。为了达到上述要求,提出了基于FPGA 的高性能DAC 芯片回路测试法。

1 DAC 主要技术参数

DAC 的主要技术参数基本上可以分为静态特性参数和动态特性参数。DAC 的静态特性参数用来确定其转换的度,主要包括失调误差(Offset Error)、增益误差(Gain Error)、积分非线性误差(INL)以及微分非线性误差(DNL)等。DAC动态特性参数用来确定其交流条件下的性能,主要包括信噪比(SNR)、信号噪声和失真比(SINAD)、有效位数(ENOB)、总谐波失真(THD),以及无杂散动态范围(SFDR)等。

2 测试方案

2.1 设计原理

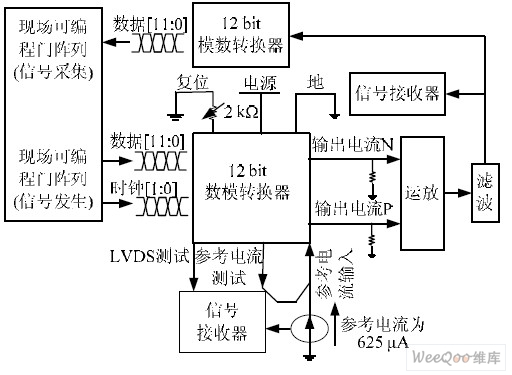

DAC 芯片参数回路测试法,就是将待测信号形成一个完整的信号回路。首先,使用FPGA 产生待测信号,经过DAC芯片后转换成模拟信号,再经过滤波、放大电路和ADC 芯片转换成数字信号,存储在FPGA 的RAM 里,然后使用QuartusII 软件Signal tap II 工具取出数据,导入Matlab 软件后,就可以对数字信号进行分析和计算,从而得到DAC 的技术参数[6]。在ADC 采样之前使用模拟信号接收器,如示波器、频谱仪等,可与后端测试结果比较分析。设计原理如图1 所示。

由于FPGA 使用非常灵活,通过配置不同的编程数据可以产生不同的电路功能,对于不同分辨率和采样速度的DAC芯片都可以进行参数测试;滤波和运算放大电路尽可能地降低信号在转换和传递过程中的噪声;数字信号在分析和计算方面比模拟信号更加准确,保证了测试系统的度;相对于其他DAC 测试系统来说,本测试方案使用的元器件比较少,成本比较低。

图1 设计原理

2.2 硬件实现

DAC 使用12 位分辨率、250 Ms/s 采样速度的DAC 芯片,芯片采用LVDS 差分电路、PTAT 基准源以及4+4+4 电流源阵列等关键技术设计,可以满足高速高分辨率转换电路处理的要求。FPGA 是Altera 公司Cyclone III 系列EP3C25Q240C8 芯片,功耗小,系统综合能力强,价格较低,包含了24*个逻辑单元、594 Kbit 内存空间和4 个锁相环,硬件资源完全可以满足测试的要求[8] 。ADC 是LINEAR 公司的LTC2242-12 芯片,交流特性非常好,降低了测试系统带来的误差。运算放大器是ADI 公司的AD8008 芯片,非常好的驱动特性保证了DAC 芯片输出信号的质量,提高了DAC 的驱动能力。

2.3 软件设计

软件代码采用硬件描述语言Verilog实现。FPGA产生待测信号包括Test(全零、全一等)、Ladder(阶梯波)和Sin(正弦波)。其中Test信号用于测试DAC芯片的静态特性参数失调误差和增益误差,Ladder信号用于测试DNL和INL,Sin信号用于测试动态特性参数SNR、SINAD、ENOB、THD和SFDR。

数据分析和计算过程主要通过Matlab 软件实现。DAC 芯片输入全零和全一信号,可计算出失调误差和增益误差;使用阶梯波信号测试INL 和DNL 时,为了测试度,将12位输入数据分成高中低各四个位进行测试。DAC 的动态特性参数测试采用快速傅里叶变换的方法,将Signal tap II 工具取出数据经过FFT 和其他运算,得到SNR、SINAD、ENOB、THD 和SFDR 等动态特性参数,它们可以全面地反映DAC 的动态特性,这里到14 阶谐波。

3 测试结果

Test 信号测试:DAC输入全一状态的输出电压为760 mV,输入全零状态的输出电压为276 uV,经过Matlab 计算,失调误差是0.036%,增益误差是3.63%。

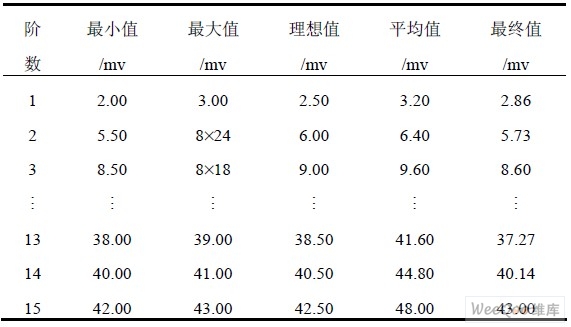

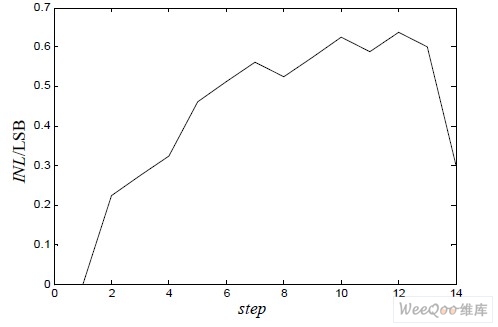

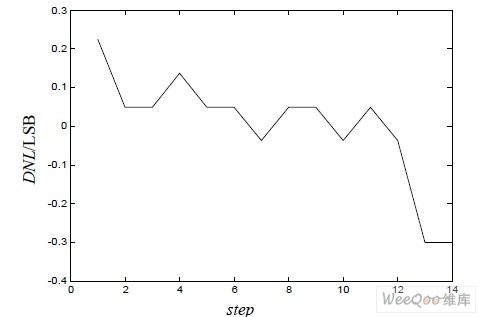

Ladder 信号测试:在计算INL 和DNL 时,DAC 输入高中低各四个位的测试原理相同,以中四位为例来介绍。n=12,i 从24~28 位变化,用1LSB 来表示,测定输出的15 次(Step)阶梯波,转换成电压值,部分数据如表1 所示,每列数据分别表示阶数、测试值、测试值、测试平均值、理想数值以及考虑小电流影响后终电压值。使用Matlab 软件分析数据后得到INL 和DNL 曲线如图2 和图3 所示。

表1 15 次阶梯波电压值

图2 INL 分析曲线

图3 DNL 分析曲线

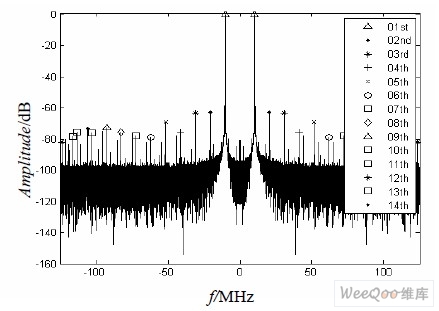

Sin 信号测试:输入正弦波频率25 kHz,AD 采样率为100 MHz/s,输出数字信号经过Matlab 分析计算后,测得SNR是58 dB,SINAD 是57.75 dB,SFDR 是62.84 dB,THD 是58.62 dB,ENOB 是9.3 位。时域波形和FFT 变换后14 阶谐波的频谱如图4 和图5 所示。

图4 sin 信号输出时域波形

图5 sin 信号输出频域波形

4 结语

以12 位、250 Ms/s DAC 芯片为例,在FPGA 的基础上使用回路测试法,测试了其静态特性参数和动态特性参数。实验结果表明,可以有效地测试DAC 芯片的静态特性参数和动态特性参数。同时可以测试不同分辨率和采样速度的DAC 芯片,测试结果比普通模拟测试仪器的高,测试系统比专用DAC 自动测试设备成本低。

参考文献:

[1]. LVDS datasheet https://www.dzsc.com/datasheet/LVDS+_457917.html.

[2]. AD8008 datasheet https://www.dzsc.com/datasheet/AD8008+_2043575.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PLC的34个基础知识2024/1/17 16:25:58

- 印刷电路板的组装方法2023/9/15 17:04:46

- 模拟量输入测量值显示满量程(上溢)的故障处理方法2023/8/31 11:09:13

- 什么是PLC?看完就明白2023/5/5 16:37:01

- 可编程逻辑控制器 (PLC) 中的梯形逻辑2023/4/23 15:48:34