ADSP-BF533系统设的计和实现

出处:现代电子技术 发布于:2011-06-08 11:43:29

1引言

ADSP-BF533处理器是AD公司生产的Blackfin系列数字信号处理器产品的成员。基于ADSP-BF533的系统实现了DSP的基本功能,在科研、教学和工程等领域有着广泛的应用。主要介绍了基于ADSP-BF533的系统硬件电路设计方案,包括电源电路、时钟电路、复位电路、存储器扩展电路和JTAG接口电路,并阐述了在电路设计过程中需要注意的事项,为DSP技术的应用提供了一个良好的平台。

ADSP BF533 是ADI 公司推出的嵌入式多媒体处理器,拥有运算频率高达750 MHz 的DSP 内核;采用ADI公司与Intel 公司共同开发的MSA 体系结构[(微信号结构) ,这种结构采用了一个综合的信号处理和控制指令集。这样处理器就不仅是带有增强指令集的DSP ,也不仅是带有2 个算术逻辑单元的MCU ,而是为同时运行控制指令和算术指令而进行优化的处理器结构,集DSP 和MCU功能于一身,从而消除了传统的多个不同处理器之间联系的复杂性。ADSP BF533 处理器具有以下特点:

①处理器支持与分级存储结构相结合的改进型哈佛结构,时钟频率为600 MHz , 峰值处理能力为1. 2GMIPS。通过对工作频率及电压的动态调节可实现极低的功耗。动态电源管理完全是由软件实时控制的,可以在运行时随时改变内核电源,以降低功耗,效果非常明显。

②ADSP BF533 DSP 内核包括2 个40 位的算术逻辑单元(ALU) 、2 个乘法器累加器(MAC) 、4 个视频ALU和1 个移位器。ADSP BF533 的硬件结构具有很高的并行性和运算能力,可以进行双16 位数的加减、交叉和移位运算,在设计中可以提高运算速度,并使复数运算大大简化。

③处理器的指令集包含了大量的运算指令,可以快速执行固定点和小数运算,如乘加器和MAC shift 指令等。

④处理器可以实现零开销硬件循环,其效率比通过条件分支返回循环起点的方式高得多。

⑤处理器将成组的寄存器与函数单元相关联,从而加快了运行速度、降低了功耗。例如,Blackfin 处理器既有运算寄存器或d2reg 寄存器,又有地址寄存器或preg 寄存器。

⑥DMA 数据的重排功能可以优化图像数据在内存中的存储,这不仅可以提高内部存储空间的利用效率,也可以提高数据的传输效率。虽然图像数据的传输也可由软件实现,但会消耗大量的CPU 时钟周期,从而使DSP的高速性能难以发挥,而由DMA 来完成同样的工作却不占用CPU 的时钟周期。

2系统总体设计

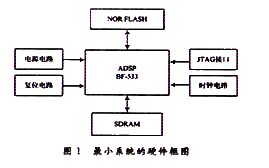

系统是由保证处理器可靠工作所必须的基本电路组成的,主要包括电源电路、时钟电路、复位电路、SDRAM、FLASH存储器和JTAG接口电路组成,其硬件框图如图1所示。

2.1 电源电路

BF-533外部IO供电电压为3.3 V,内核供电电压为1.2 V。因此,系统采用双电源输出方案,采用TPS73HD301作为电源芯片,典型输入电压为+5 V,输出电压为+3.3 V和+1.2 V,每个输出可提供750 mA的电流。TPS73HD301具有电压监控功能,以保证被供电芯片在一个恒压下正常工作。他为每一路电压输出提供一个复位输出口,当他检测到输出的电压为欠压状态时,与那个输出电压相对应的RESET管脚将输出一个低电平,以启动系统复位。其电路如图2所示。

2.2 时钟电路

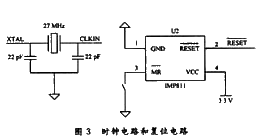

BF-533可以使用外部时钟,也可以使用内部振荡电路。当使用外部时钟时,应将此外部时钟连接到DSP的CLKIN引脚,且XTAL引脚悬空。本系统采用的是内部振荡电路外接晶振的方式,晶振连接到CLKIN和XTAL之间,并与两个电容相连,如图3所示。

2.3 复位电路

手动复位是系统常用的功能,本系统采用专用复位芯片IMP811实现手动复位,如图3所示。

2.4 JTAG接口电路

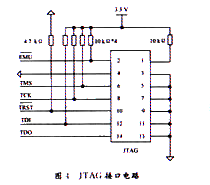

BF-533提供了一个1EEE 11 49.1 JTAG测试访问端口。通过此端口,仿真器能够访问DSP的内部,允许开发者装载代码,设置断点,观察变量和寄存器。本系统采用14针接口的标准,如图4所示。

2.5 SDRAM

SDRAM(同步动态随机存储器)具有随机读写速度快,写入数据之前不需要进行擦除的特点,在嵌入式系统中成为不可缺少的存储设备之一。本系统采用HY57V561620,其容量为32 MB,频率为133 MHz。ADSP-BF533支持与SDRAM的无缝连接,SDRAM的地址映射为OX00000000~OX080000000,其连接方法如图5所示。

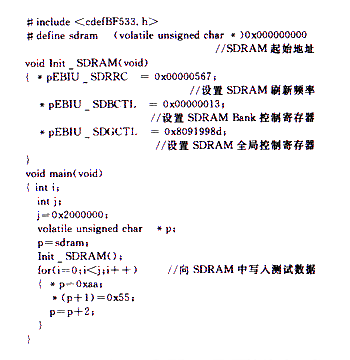

对于SDRAM可以采用以下程序进行测试:

该程序将0x2000000个数写入SDRAM,在Visual DSP++的BLACKFIN Memory窗口可以观察到SDRAM的数据写入情况,以验证写入是否正确。

2.6 FLASH存储器

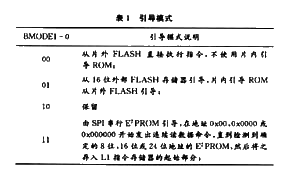

ADSP-BF533具有3种引导模式,如表1所示。当上电复位或者软件初始化复位后,处理器采样复位配置寄存器BMODE引脚,执行引导功能。无论采取何种引导模式,都要从外部存储器设备首先读取一个10个字节的头。这个头指定将被传输的字节数量和存储器的目的地址。多存储器模块可被任何引导次序装载,一但所有模块被装载,程序从L1指令SRAM的起始部分开始执行指令。

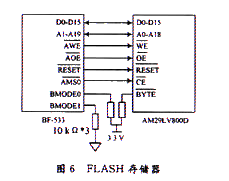

本系统采用NOR FLASH作为引导代码存储器,选用容量为1 MB的AM29LV800D,将其接在BF-533异步存储空间的BANK0上,其地址范围为0x20000000~0x20100000,电路如图6所示。

3系统设计注意事项

(1)对于没有用到的DSP引脚,应将其拉高、拉低,或者定义成输出端,例如如果nBR,ARDY引脚不用时应拉高,RTXI,NMI引脚不用时应拉低。

(2)在电路板设计中,应在电源和地之间合理分布去耦电容,以滤除噪声,提高系统的稳定性。

(3)尽量缩短高频信号的走线,时钟和负载的连线尽量短而粗,并且晶振下面不要走线。

4 结 语

系统可以直接作为部件应用与工程和科研中,具有良好的通用性和可扩展性。在系统的基础上,可以很方便地进行二次开发和功能扩展,能够缩短开发周期,降低开发成本。本文实现了系统的基本功能,介绍了各模块的硬件电路,为DSP应用技术的研究提供了一个良好的平台。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 模糊逻辑在 DSP 上实时执行2023/7/25 17:13:30

- 多速率DSP及其在数模转换中的应用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系统的信号完整性2022/9/26 16:45:38

- 自适应噪声消除系统的实现2022/1/17 17:51:17