基于FPGA的通用位同步器设计方案(一)

出处:电子爱好者博客 发布于:2013-10-12 10:00:01

摘要本文提出了一种基于FPGA的通用位同步器设计方案。方案中的同步器是采用改进后的Gardner算法结构,其中,内插滤波器采用系数实时计算的Farrow结构,定时误差检测采用独立于载波相位偏差的GA-TED算法,内部控制器和环路滤波器的参数可由外部控制器设置,因而可以适应较宽速率范围内的基带码元。

本文主要是先阐述传统Gardner算法的原理,然后给出改进后的设计和FPGA实现方法,对结果进行仿真和分析,证明该设计方案的正确、可行性。

0 引言

数字通信中,位同步性能直接影响接收机的好坏,是通信技术研究的重点和热点问题。通信系统中,接收端产生与发送基带信号速率相同,相位与判决时刻一致的定时脉冲序列,该过程即称为位同步。常见的位同步方法包括滤波法和鉴相法。滤波法对接收波形进行变换,使之含有位同步信息,再通过窄带滤波器滤出,缺点是只适用于窄带信号。为常用的位同步方法是鉴相法,包括锁相法和内插法两种。锁相法采用传统锁相环,需要不断调整本地时钟的频率和相位,不适合宽速率范围的基带码元同步。而内插法则利用数字信号的内插原理,通过计算直接得到判决点的值和相位。

Gardner算法即是基于内插法的原理,通过定时环路调整内插计算的参数,从而跟踪和锁定位同步信号,该算法的优点在于不需要改变本地采样时钟,可以适应较宽速率范围内的基带信号,因而具有传统方法不可替代的优势。Gardner算法的实现方法,为算法的应用提供了基础。Farrow结构非常适合实现Gardner算法的,即内插滤波器部分,其优点是资源占用较少,且滤波器系数实时计算,便于内插参数调整。定时误差检测,但在定时误差检测时需要信号中存在判定信息,并且对载波相位偏差敏感。不足进行了改进,提出了GA-TED(Gardner Timing Error Detection)算法,其优点是不需要预知判定信息,且独立于载波同步,并且适合FPGA 实现。改进的Gardner 算法,并将其应用于M-PSK 系统。提高了Gardner 算法的抗自噪声能力,即降低了对本地时钟的要求。

本文基于FPGA 平台并采用Gardner 算法设计,其中,内插滤波器采用Farrow 结构,定时误差检测采用GA-TED算法。同时对传统Gardner算法结构进行了改进,使环路滤波器和NCO的参数可由外部控制器设置,以适应不同速率的基带码元,实现通用的位同步器的设计方案。此外,本设计方案还对FPGA 代码进行了优化,节省了大量硬件资源。进行了仿真和分析,给出了仿真结果,证实了该方案的可行性。

1 传统Gardner 算法与改进

1.1 传统Gardner算法基本原理

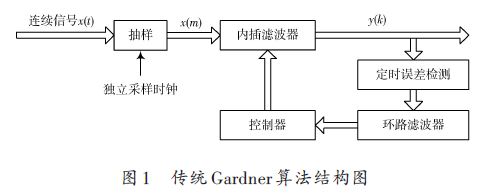

传统Gardner算法结构如图1所示。

在图1中,输入的连续时间信号x(t) 码元周期为T,频带受限。在满足奈奎斯特定理的条件下,接收端采用独立时钟对x(t) 进行采样。内插滤波器计算出内插值y(k),送至定时环路进行误差反馈和参数调整,并与控制器输出的位同步脉冲BS一起送往解调器的抽样判决器。

定时环路包含定时误差检测、环路滤波器和控制器。定时误差检测提取插值时刻和判决时刻的误差;该误差经环路滤波器滤除高频噪声后送给控制器;控制器计算插值时刻(即为位同步信号的2倍频)和误差间隔。插值时刻和误差间隔用于调整内插滤波器的系数,使插值时刻尽可能与判决点同相,终实现位同步信号的提取。

1.2 改进的Gardner算法结构

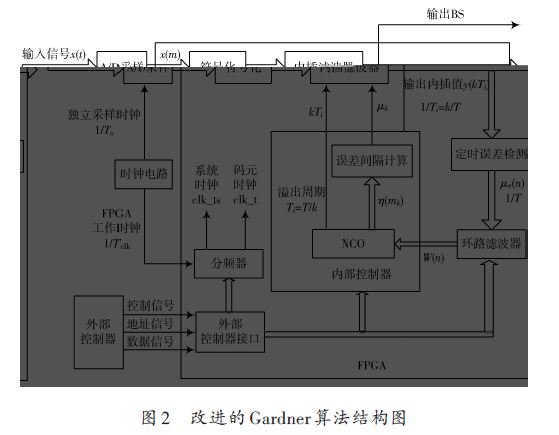

从上节可以看出,传统Gardner算法无法满足较宽速率范围基带信号的位同步要求。为实现该要求,本设计在FPGA 平台的基础上,对算法实现结构进行了改进,改进结构如图2所示。

图2中,内插滤波器采用Farrow结构的FIR 滤波器实现,滤波器系数实时计算;定时误差检测采用独立于载波且采样点较少的GA-TED 算法;环路滤波器、内部控制器可由外部控制器设置参数,基带码元速率变化时,相应参数可以随之变化。因此,本设计可以满足位同步器的通用性要求。

该同步器工作过程如下:外部控制器根据基带码元速率设置相应参数,通过外部控制器接口将控制、地址和数据信号分别送往分频器、环路滤波器和内部控制器。时钟电路分别提供采样时钟和FPGA 时钟,FPGA工作时钟在片内通过分频器产生所需频率的时钟,供FPGA 各模块使用。输入连续时间信号x(t) 经由独立时钟控制的ADC 进行采样,转换为8 位数字信号送至FPGA 内,符号化后变为有符号数字序列,送入内插滤波器模块。内插滤波器根据输入信号的采样值和内部控制器给出的参数μk,在每个插值时刻kTi 计算出判决点的内插值y(kTi)。定时误差检测计算出误差μτ (n),输出至环路滤波器。环路滤波器依据当前的参数设定,滤除噪声并将误差信息送给内部控制器。内部控制器以NCO为,根据处理后的误差信息和设定的频率字参数调整插值时刻kTi,使之尽可能接近判决时刻,并输出位同步脉冲BS,同时计算出误差间隔μk 送给内插滤波器,进行内插值计算,终完成定时信息的恢复。

2 FPGA设计

2.1 整体结构设计

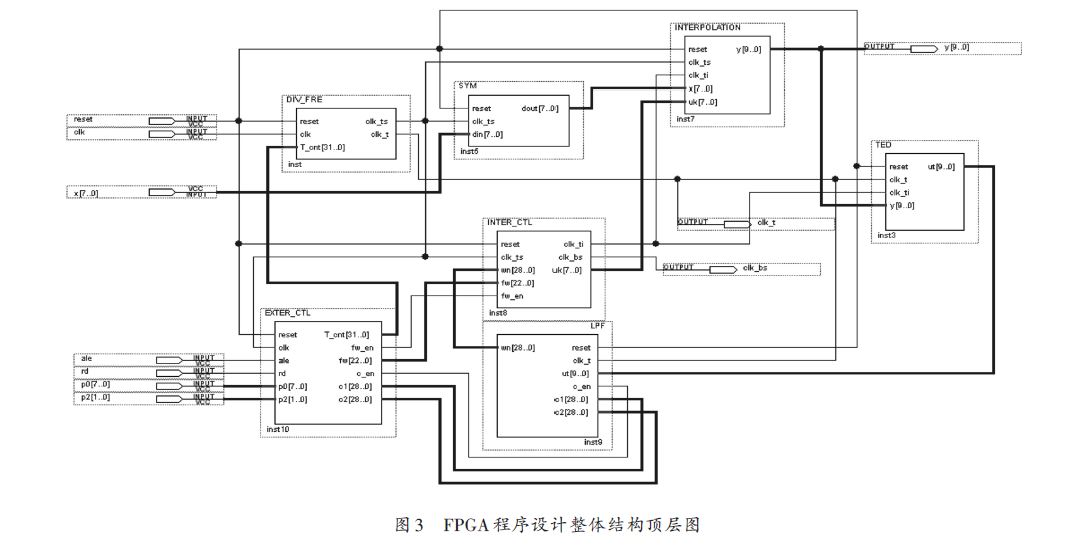

根据图2的算法结构,FPGA设计采用模块化方式,整体结构的顶层图如图3所示。

从图3可以看到,该设计包含分频器(DIV_FRE)、符号化(SYM)、内插滤波器(INTERPOLATION)、定时误差检测(TED)、环路滤波器(LPF)、内部控制器(INTER_CTL)和外部控制器接口的时序电路(EXTER_CTL)共7个模块。其中,分频器由片外晶振提供时钟输入,分频后为片内其他模块提供相应时钟。其中码元时钟的分频系数可由外部控制器通过接口进行设置。符号化是将A/D采样产生的无符号数转换为有符号数,以便后续模块进行带符号的运算。

外部控制器接口的时序电路将外部控制器送来的控制信号(ALE和RD)、地址信号(P2.0、P2.1)和数据信号(P0口)、转换为FPGA 内分频器、环路滤波器和NCO的使能信号和参数,实现对位同步器各参数的设置。

分频器、符号化和外部控制器接口模块实现较为简单,不再赘述。而内插滤波器、定时误差检测、环路滤波器和内部控制器的实现较为复杂,且本设计通过采用相应算法和改进结构,实现了位同步器的通用性。本文将详细阐述这些模块的设计。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PLC的34个基础知识2024/1/17 16:25:58

- 印刷电路板的组装方法2023/9/15 17:04:46

- 模拟量输入测量值显示满量程(上溢)的故障处理方法2023/8/31 11:09:13

- 什么是PLC?看完就明白2023/5/5 16:37:01

- 可编程逻辑控制器 (PLC) 中的梯形逻辑2023/4/23 15:48:34