基于VLSI平台的MIPS处理器仿真与设计

出处:电子爱好者博客 发布于:2013-07-22 11:42:27

摘要:传统ISA处理器由于其内部有限的逻辑资源和外部固定的引脚封装,大大地限制了它的应用范围。使用硬件描述语言,自底向上设计处理MIPS,并且与几类通用外设互连组成系统,使用Virtex-Ⅱ Pro系列FPGA进行板级验证。

板级验证结果表明实现了既定目标,与标准MCU 兼容,系统运行稳定。这样可以依据自己的需求,定制系统以达到传统MCU所无法完成的要求。

0 引言

随着社会的发展,工业控制及人们日常生活越来越追求精密控制,为了满足这种需求,微控制器得到了快速的发展。随着VLSI 发展,MCU 将原本分散的CPU,RAM,ROM,I/O等集中于一块单晶芯片内,形成一种芯片级计算系统。MCU 主要用于控制目的,MCU 构成的系统有实时、快速的外部响应,能迅速采集到大量的数据,做出逻辑判断与推理后实现对被控制对象的参数调整与控制。

但是随着时代的推进,对控制的要求逐步增大,所需满足功能的逐渐增多,传统MCU 也越来越显得捉襟见肘。尤其是面对现代SoC 的挑战。为此,使用ASIC器件在片内实现与传统MCU 相兼容的,选用合适的片内总线来连接外设,构成一个兼容传统MCU平台,这种方法必会延续传统MCU 的生命力,使其获得更大的发展。

1 Virtex-Ⅱ Pro

Virtex-Ⅱ Pro系列在Virtex-Ⅱ的基础上,增强了嵌入式处理能力,内嵌PowerPC405内核,还包括了先进的主动互联技术,以解决高性能系统所面临的挑战。此外还增加了高速串行收发器,提供了千兆以太网的解决方案。主要特征如下:

(1)核电压为1.5 V,工作时钟可以达到420 MHz;(2)支持多达20种的I/O接口标准;(3)增加了2个高性能RISC技术,频率高达400 MHz的PowerPC处理器;(4)增加多个3.125 Gb/s 速率的Rocket 串行收发器;(5)内嵌了多个硬核乘法器,提高了DSP处理能力;(6)具有完全系统时钟管理功能,多达8个DCM.

2 Virtual MIPS Core 实现

Virtual MIPS Core 依据MIPS 公司的32 位处理器R3000实现,采用3级流水线技术,其结构如图1所示。

主要分为:CPU模块、Cache模块和外设总线接口模块。

其中CPU模块实现了MIPS R3000处理器中简单的CP0功能,由总线控制机构、流水线机构、冒险处理机构、异常处理机构、运算机构和译码机构等组成。

2.1 总线控制机构

Virtual MIPS Core采用哈佛结构,有三条分离的总线:程序总线、数据读总线和数据写总线。采用该种总线方式允许CPU在执行操作码时对数据进行读取或写入操作。这完全避免了冯诺依曼瓶颈,大大提高了系统的速率,而且在实现也较为简单,重要的是,允许连接高速缓存(Cache)。但是数据读总线和数据写总线共用一组地址总线,这点使得无法在同一时刻进行数据的存储和读取操作,造成了一定的限制。

2.2 指令译码结构

模拟MIPS R3000处理器,支持的是MIPS-I指令,指令有三种格式:I格式,J格式,R格式。每种格式都由若干字段组成,其指令格式如图2所示。

其中:OP:操作码;rs:个源操作寄存器;rt:

第二个源操作寄存器;rd:目的操作寄存器;shamt:位移量;funct:函数。

MIPS 指令集主要分为:存储指令、读取指令、算术运算指令、逻辑运算指令、条件分支指令和跳转指令。

2.3 ALU

采用模块化设计,分为3个模块:控制模块、加减法模块、乘除法模块。控制模块负责简单的控制功能,如功能选择等;在本设计中加法功能使用超前进位法来设计,而减法功能则使用加补码的方式通过加法功能实现;XILINX 公司提供了很多关于乘除法运算的高效的IP核,其具体方法可参考文献。

2.4 异常处理机构

Virtual MIPS Core参照MIPS R3000设计,目前实现了2 条软件异常指令SYSCALL 和BREAK.当异常到达,CPU将保存环境于EPC寄存器中,并且更新SR等寄存器,放弃流水线中的指令,直接跳转到异常处理函数地址,执行异常处理函数。

2.5 流水线机构

Virtual MIPS Core参照MIPS R3000微处理器设计,采用三级流水线结构:

Stage 0:FETCH,给出指令地址,并且读取相应的指令,主要由译码机构负责;Stage 1:ALU/MEM,ALU 运算,或者数据存储器操作,读数据存储器时,在地址总线上给出正确的值,当写数据存储器时,不仅需要提供正确的地址,还需要在数据总线上提供正确的数据,主要由运算机构和总线控制机构负责;Stage 2:LOAD,从数据线上获取数据,存至寄存器中,主要由寄存器机构负责。

由于MIPS 的RISC 结构,可方便的实现流水线,它的程序存储器和数据存储器分离总线结构,使得能够可以同时进行取指令操作和数据操作,如图3所示。

2.6 冒险处理机构

在Virtual MIPS Core 中引入了Pipeline 技术,在提高效率的同时,也引入了竞争冒险。这里主要关注两类冒险现象:

数据冒险,假如一条指令需要访问某个寄存器,而该寄存器会被前一条指令更改,此时便发生了数据冒险。

资源冒险,该冒险主要发生在数据存储器操作上,当一条指令装载数据至某个寄存器中,而装载过程会有延迟,在这个延迟过程中,下条指令使用了该寄存器,由于装载的未完成,造成了资源上的冒险。

针对数据冒险,解决方式是增加一点前馈逻辑电路,一旦检测到数据冒险,使用前馈值来取代寄存器读取值。对于解决资源冒险,采用的是软件解决方法。使用的是普通标准MIPS编译器如MIPS-GNU-LINUX-GCC等来产生二进制可执行程序,而这些编译器都可以自动插入NOP指令,为保证数据读取的完整,编译器可以自动的在每条装载指令后插入NOP,以达到数据的完整性。

可以详细列出三级流水线中所需完成的动作:

2.7 REG

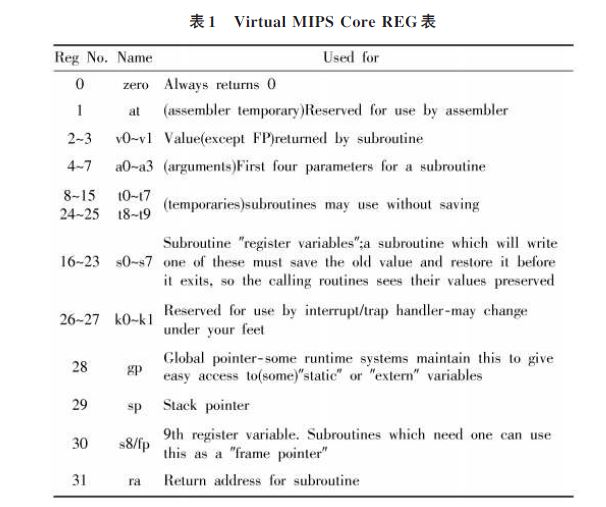

Virtual MIPS Core将REG模块分离设计,这样方便管理,实现了标准R3000的寄存器,见表1.

2.8 Cache

为了能够尽量与MIPS R3000 处理器一致,使用FPGA 中LUT 配置2 个Cache:I-Cache(指令告诉缓存)和D-Cache(数据告诉缓存);为了简化设计,使用直接映射的方式设计了Cache,对于D-Cache采用写直达方式,虽然效率不一定很高,但是确实是容易实现的,详见参考文献。注意,在写直达的过程中,会将CPU挂起,直到数据存储器更新完毕,虽然将会造成CPU效率的下降,但这样能够避免Cache和数据存储器中的数据不同步问题,实现也较为简单。

3 测试

硬件环境主要分为两部分组成:

部分为板,使用Virtex-Ⅱ Pro 系列中的XC2VP50FFG1152 芯片作为的FPGA,在FPGA 外围又添加了DDR 和SDRAM.因为FPGA 掉电后,内容自动消失,每次上电需要重新配置,为了让FPGA 上电后自动配置,需要增加一片PROM,使用的是XCF32P,该芯片容量达到32M,支持多种工作模式。FPGA 采用并行主模式。

第二部分为底板,增加了大量的外设:UART,PS2,VGA,ETHERNET,VIDEO,AD/DA,SD,USB等。

3.1 测试工具

为了能够很好地更新ROM 中的数据,首先要做的是将BRAM 配置为双端口RAM,一端口给Virtual Core来进行读取操作,一端口提供给EDK,用来更新程序存储器;同时EDK 也可以提供简单的控制任务,如重启Virtual Core 等,EDK 使用UART 来和计算机进行操作。EDK操作流程如图4所示。

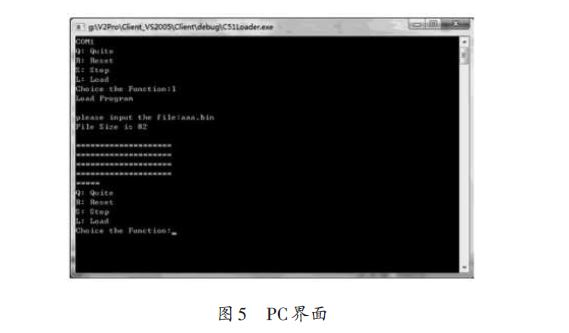

为了方便控制,设计了一个较为简易的PC 端串口程序,用于将EDK 与PC 交互。其工作过程较为简单,主要是将用户的命令或者文件经串口发送至EDK,其截屏如图5所示。

3.2 Virtual MIPS 测试

搭建一个简易系统,进行测试,使用ISE布局布线,其资源消耗如图6所示。

编写一段测试程序,用于测试其运行状况,其代码如下:

使用mips-linux-gnu-gcc 编译工具编译生成HEX文件后,转为BIN 文件,将BIN 文件加载至ROM 中运行,结果如图7所示,与理论计算一致,因此实验通过。

4 结论

本文从Virtual MIPS Core开始,详细阐述了用FPGA虚拟出传统MCU的设计原理和方法。在教学方面这种方式有利于开展计算机体系结构教学实验。使用VirtualMIPS微处理器,开展如下实验:MIPS指令集译码过程设计实验;ALU单元设计实验;流水线技术实验;Cache机制的实验等。在工业设计方面使用这种方式,可以充分地利用市场上已经成熟的外设核,避免造成重复设计,同时使用这种结构,也可以方便对传统的MCU进行裁剪和定制,这样将会使传统的MCU更加的灵活可变。

下一篇:微秒级宽带高速捷变频技术研究

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- cps是什么意思?cps的含义_cps的特征2024/4/16 17:56:11

- 你所知道的DCS系统都有哪些?2024/4/16 17:50:53

- 煤矿人员定位系统的功能及重要性分析2024/4/16 17:43:54

- 什么是冗余?2024/4/15 17:33:02

- linuxfind命令详解2024/4/15 17:27:22