74LVTH16646 Low Voltage 16-Bit Transceiver/Register with 3-STATE Outputs

January 2000

Revised January 2000

74LVTH16646

Low Voltage 16-Bit Transceiver/Register

with 3-STATE Outputs

General Description

The LVTH16646 contains sixteen non-inverting bidirec-

tional registered bus transceivers providing multiplexed

transmission of data directly from the input bus or from the

internal storage registers. Each byte has separate control

inputs which can be shorted together for full 16-bit opera-

tion. The DIR inputs determine the direction of data flow

through the device. The CPAB and CPBA inputs load data

into the registers on the LOW-to-HIGH transition (see

Functional Description).

The LVTH16646 data inputs include bushold, eliminating

the need for external pull-up resistors to hold unused

inputs.

These transceivers are designed for low-voltage (3.3V)

V

CC

applications, but with the capability to provide a TTL

interface to a 5V environment. The LVTH16646 is fabri-

cated with an advanced BiCMOS technology to achieve

high speed operation similar to 5V ABT while maintaining

low power dissipation.

Features

s

Input and output interface capability to systems at

5V V

CC

s

Bushold data inputs eliminate the need for external

pull-up resistors to hold unused inputs

s

Live insertion/extraction permitted

s

Power Up/Down high impedance provides

glitch-free bus loading

s

Outputs source/sink

鈭?2

mA/+64 mA

s

Functionally compatible with the 74 series 16646

s

Latch-up performance exceeds 500 mA

Ordering Code:

Order Number

74LVTH16646MEA

74LVTH16646MTD

Package Number

MS56A

MTD56

Package Description

56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300 Wide

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter 鈥淴鈥?to the ordering code.

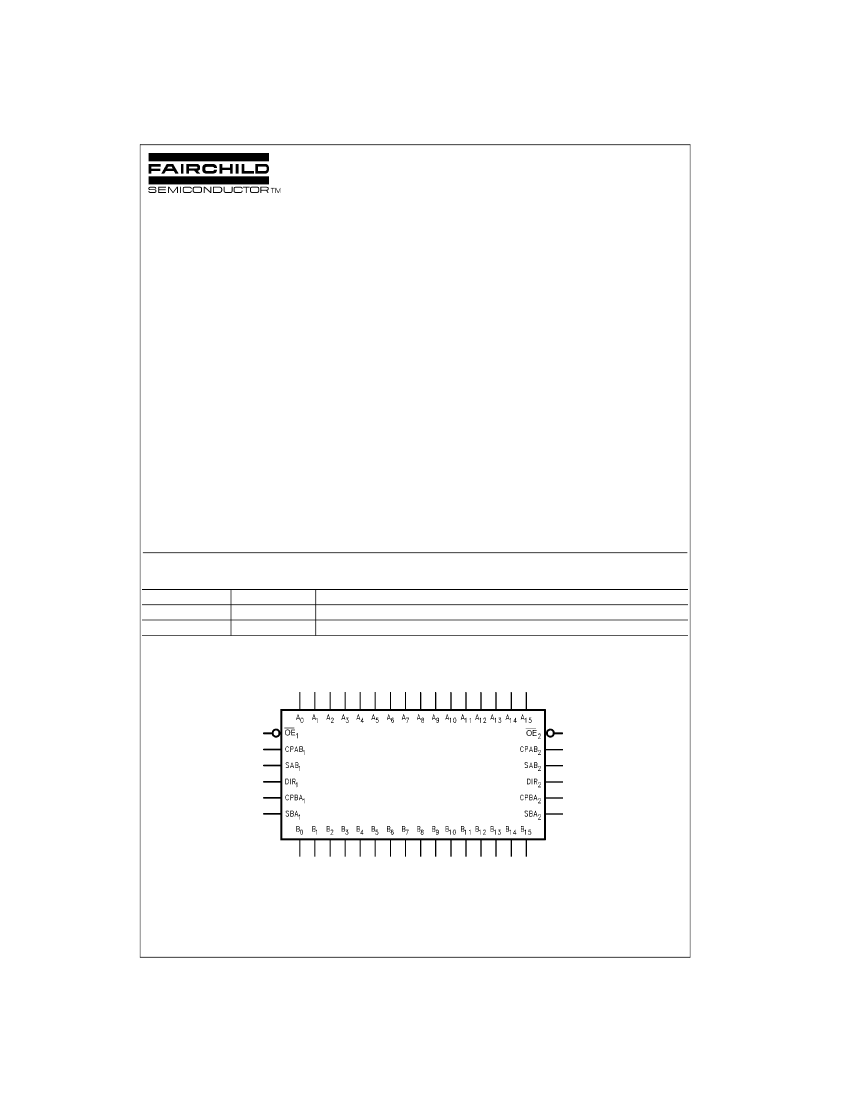

Logic Symbol

漏 2000 Fairchild Semiconductor Corporation

DS012023

www.fairchildsemi.com