鈥?/div>

I

SB

= 6 mA

Fully asynchronous and simultaneous read and write

operation

Empty, Full, and Programmable Almost Empty and Al-

most Full status flags

Retransmit function

Output Enable (OE) pin

Independent read and write enable pins

Supports free-running 50% duty cycle clock inputs

Width Expansion Capability

Depth Expansion Capability through token-passing

scheme (no external logic required)

64-pin 10x10 STQFP

Pin-compatible 3.3V solution for CY7C4282/92

Functional Description

The CY7C4282V/92V are high-speed, low-power, first-in first-

out (FIFO) memories with clocked read and write interfaces.

All devices are 9 bits wide. The CY7C4282V/92V can be cas-

caded to increase FIFO depth. Programmable features include

Almost Full/Almost Empty flags. These FIFOs provide solutions

for a wide variety of data buffering needs, including high-speed data

acquisition, multiprocessor interfaces, video and communications

buffering.

These FIFOs have 9-bit input and output ports that are con-

trolled by separate clock and enable signals. The input port is

controlled by a free-running clock (WCLK) and a Write Enable

pin (WEN).

Retransmit and Synchronous Almost Full/Almost Empty flag

features are available on these devices.

Depth expansion is possible using the Cascade Input (XI), Cas-

cade Output (XO), and First Load (FL) pins. The XO pin is connected

to the XI pin of the next device, and the XO pin of the last device

should be connected to the XI pin of the first device. The FL pin of the

first device is tied to V

SS

and the FL pin of all the remaining devices

should be tied to V

CC

When WEN is asserted, data is written into the FIFO on the

rising edge of the WCLK signal. While WEN is held active, data

is continually written into the FIFO on each cycle. The output

port is controlled in a similar manner by a free-running Read

Clock (RCLK) and a Read Enable pin (REN). In addition, the

CY7C4282V/92V have an Output Enable pin (OE). The read

and write clocks may be tied together for single-clock operation

or the two clocks may be run independently for asynchronous

read/write applications. Clock frequencies up to 67 MHz are

achievable.

D

0

鈭?/div>

8

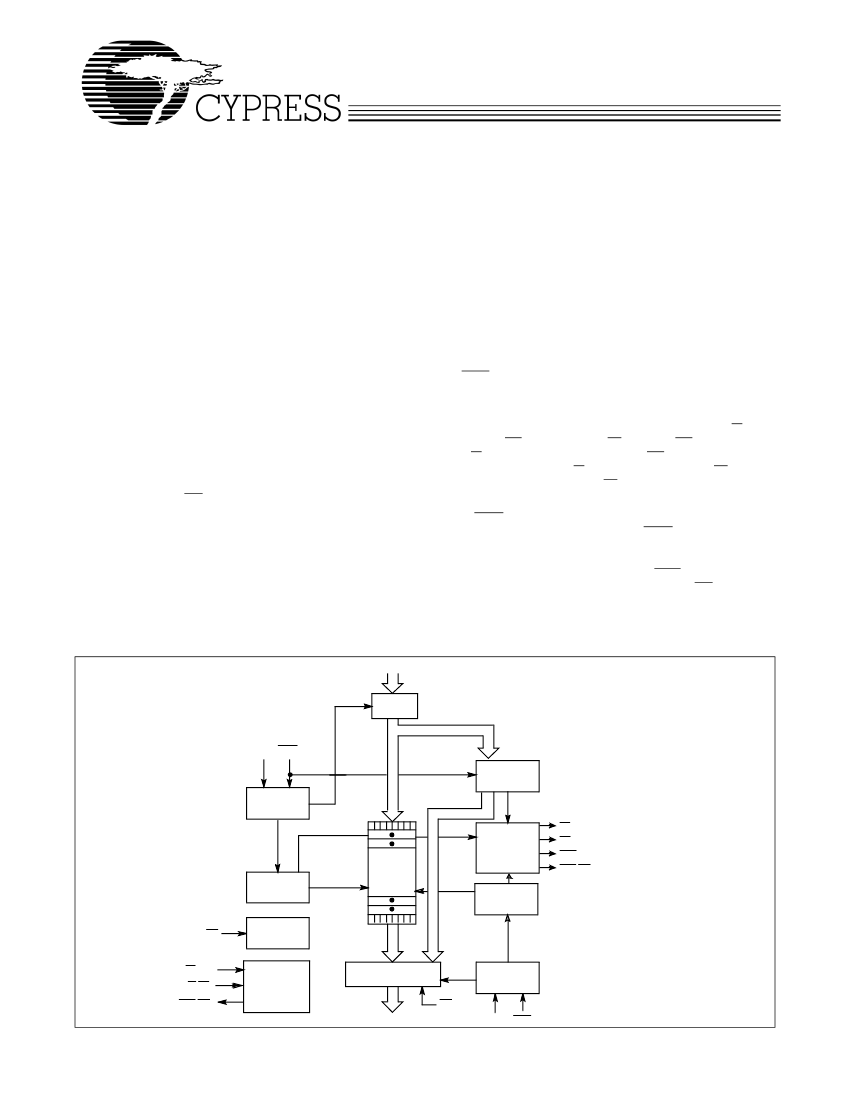

Logic Block Diagram

INPUT

REGISTER

WCLK WEN

FLAG

PROGRAM

REGISTER

WRITE

CONTROL

FF

FLAG

LOGIC

Dual Port

RAM Array

64K x 9

128K x 9

READ

POINTER

EF

PAE

PAF/XO

WRITE

POINTER

RS

RESET

LOGIC

FL/RT

XI/LD

PAF/XO

EXPANSION

LOGIC

THREE-STATE

OUTPUT REGISTER

OE

Q

0

鈭?/div>

8

READ

CONTROL

RCLK REN

4282V鈥?

Cypress Semiconductor Corporation

鈥?/div>

3901 North First Street

鈥?/div>

San Jose

鈥?/div>

CA 95134

鈥?/div>

408-943-2600

October 18, 1999

CY7C4292V-15ASC PDF文件相关型号

CY7C441–14JC,CY7C4425-15AI,CY7C4425-25AC,CY7C4425-25AI,CY7C4425-25JC,CY7C4425-25JI,CY7C4425-35AC,CY7C4425-35AI,CY7C443–12JC,CY7C443–14JC,CY7C443–20JC,CY7C443–20JI,CY7C443–30JC,CY7C443–30JI,CY7C451-12JI,CY7C451-14JC,CY7C451-14JI,CY7C451-20JC

CY7C4292V-15ASC相关型号PDF文件下载

-

型号

版本

描述

厂商

下载

-

英文版

16K x 8/9 Dual-Port Static RAM with Sem, Int, Busy

Cypress

-

英文版

32K x 8/9 Dual-Port Static RAM

Cypress

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS [C...

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS [C...

-

英文版

16K x 8/9 Dual-Port Static RAM with Sem, Int, Busy

Cypress

-

英文版

32K x 8/9 Dual-Port Static RAM

Cypress

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS [C...

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS

-

英文版

64K/128K x 8/9 Dual-Port Static RAM

CYPRESS [C...

-

英文版

4K x 16/18 and 8K x 16/18 Dual-Port Static RAM with SEM, INT...

CYPRESS

-

英文版

4K x 16/18 and 8K x 16/18 Dual-Port Static RAM with SEM, INT...

CYPRESS [C...

-

英文版

4K x 16/18 and 8K x 16/18 Dual-Port Static RAM with Sem, Int...

Cypress

-

英文版

16K x 16/18 Dual-Port Static RAM

Cypress

-

英文版

32K/64K x 16/18 Dual-Port Static RAM

CYPRESS

-

英文版

32K/64K x 16/18 Dual-Port Static RAM

CYPRESS [C...

-

英文版

32K/64K x 16/18 Dual-Port Static RAM

CYPRESS

-

英文版

32K/64K x 16/18 Dual-Port Static RAM

CYPRESS [C...