## **BCT4302**

## **Dual SIM Card Controller**

### **General Description**

The BCT4302 is a dual SIM card control chip optimized for GSM/EDGE/GPRS/3G handsets, It provides the power conversion and signal level translation needed for advanced cell phones to interface with 1.8V and 3V SIMs. The device meets all requirements for 1.8V and 3V SIMs and contains LDO regulators to power 1.8V or 3V SIM card from a 2.7V to 5.5V input. A serial port interface(SPI) is used to control dual SIM channel individually.

The BCT4302 is available in 20-pin 3mm x 3mm QFN package. The operating temperature range is from  $-25^{\circ}$ C to  $+85^{\circ}$ C.

### **Applications**

Support dual SIM card interface GSM, EDGE, GPRS and 3G Cell Phones

#### **Features**

- ◆ CMOS Technology for dual SIM card controlling

- ♦ Control and communication through a SPI interface with baseband processor.

- ♦ Power management and control for two SIM cards

- ♦ Independent 1.8/3V VCC control for each SIM card

- ♦ Fast channel switching

- ♦ Independent clock stop mode (at high or low level) for each SIM card

- ♦ Temperature Range: -25°C to 85°C

- ♦ 8KV ESD on SIM Card Pins

- ◆ 20-pin 3mm x 3mm QFN package (Pb-free & Green available):

### ORDERING INFORMATION

| Ordering Code | Package Description | Temp Range     | Top Marking |

|---------------|---------------------|----------------|-------------|

| BCT4302B-TR   | 20-pin QFN          | –25°C to +85°C | 4302B       |

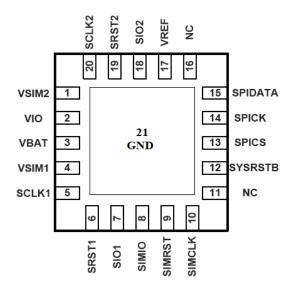

## **Connection Diagram (Top View)**

## **Pin Description**

| Pin | Name     | Description                                                  |

|-----|----------|--------------------------------------------------------------|

| 1   | VSIM2    | SIM2 Supply                                                  |

| 2   | VIO      | Digital IO Supply                                            |

| 3   | VBAT     | Battery Input Voltage                                        |

| 4   | VSIM1    | SIM1 Supply                                                  |

| 5   | SCLK1    | Level-Shifted SIM1 Clock Output                              |

| 6   | SRST1    | Level-Shifted SIM1 Reset Output                              |

| 7   | SIO1     | Level-Shifted SIM1 Bidirectional Data Input/Output           |

| 8   | SIMIO    | Non-Level-Shifted Bidirectional Data I/O                     |

| 9   | SIMRST   | Non-Level-Shifted SIM Reset Input, Internal Pull High to VIO |

| 10  | SIMCLK   | Non-Level-Shifted SIM Clock Input                            |

| 11  | NC       |                                                              |

| 12  | /SYSRSTB | System Reset, Low Active                                     |

| 13  | SPICS    | Serial bus selection                                         |

| 14  | SPICK    | Serial bus clock                                             |

| 15  | SPIDATA  | Serial bus data                                              |

| 16  | NC       |                                                              |

| 17  | VREF     | Reference Voltage Output                                     |

| 18  | SIO2     | Level-Shifted SIM2 Bidirectional Data Input/Output           |

| 19  | SRST2    | Level-Shifted SIM2 Reset Output                              |

| 20  | SCLK2    | Level-Shifted SIM2 Clock Output                              |

| 21  | GND      | Ground                                                       |

## **Detailed Description Overview**

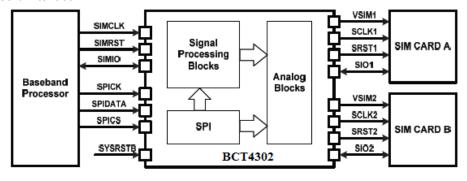

The BCT4302 is a dual SIM card control chip optimized for use with GSM baseband chipsets in handset applications. Figure 1 shows the block diagram of the BCT4302.

The BCT4302 contains several blocks:

- Serial Port Interface (SPI)

- Signal Processing Blocks

- Analog Blocks

- SIM Card Interface

Figure 1. BCT4302 Block Diagram

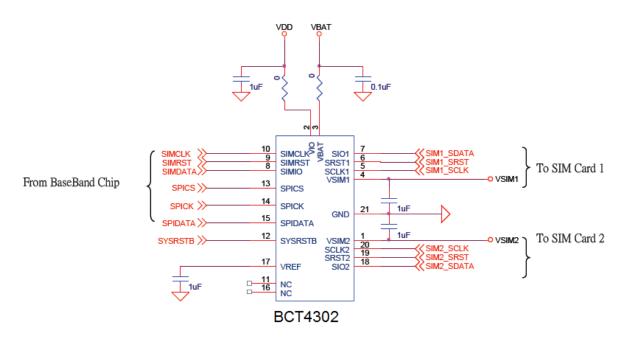

## **Application Circuit Example**

## **ABSOLUTE MAXIMUM RATINGS**(1)

| Supply Voltage $V_{CC}$                                       | Junction Lead Temperature (T <sub>L</sub> ) (Soldering, 10 seconds) |

|---------------------------------------------------------------|---------------------------------------------------------------------|

| Storage Temperature Range (T <sub>STG</sub> ) –65°C to +150°C |                                                                     |

| Junction Temperature under Bias (T <sub>J</sub> ) 150°C       |                                                                     |

Note 1:Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.

## **Electrical CHARACTERISTICS**

( VBAT=2.7V-5.5V, CVREF=CVSIM1=CVSIM2=2.2uF, minimum loads applied on all outputs, unless otherwise noted. Typical values are at TA=+25 °C, VIO=3.0V, VBAT=4.0V )

| Paramete    | er           | Condition  |           |         | Min      | Typical | Max      | Unit |

|-------------|--------------|------------|-----------|---------|----------|---------|----------|------|

| Input power | er supply    |            |           |         |          | •       | •        |      |

| VBAT        | Operating    |            |           |         | 2.7      |         | 5.5      | V    |

| Voltage     |              |            |           |         |          |         |          |      |

| VBAT        | Shutdown     | VIO=0V     |           |         |          | 0.1     | 1        | uA   |

| Current     |              |            |           |         |          |         |          |      |

| VBAT        | Operating    | VSIM1=3.0V | VSIM2=0V, | no load |          | 30      | 70       | uA   |

| Ground Cu   | rrent        | VSIM1=1.8V | VSIM2=0V, | no load |          | 30      | 70       |      |

| VIO Operat  | ting Voltage |            |           |         | 2.6      |         | 3.2      | V    |

| VIO Shutdo  | own Current  |            |           |         |          | 0.1     | 1        | uA   |

|             | ting Ground  |            |           |         |          | 3       | 5        | uA   |

| Current     |              |            |           |         |          |         |          |      |

| Input Cont  | rol          |            |           |         |          |         |          |      |

| Low Input 7 | Γhreshold    | SPIDATA,   | SPICK,    | SPICS,  |          |         | 0.15*VIO | V    |

|             |              | SYSRSTB    |           |         |          |         |          |      |

| High Input  | Threshold    | SPIDATA,   | SPICK,    | SPICS,  | 0.85*VIO |         |          | V    |

|             |              | SYSRSTB    |           |         |          |         |          |      |

| Parameter                                          | Condition                                                                                            | Min             | Typical  | Max          | Unit    |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|----------|--------------|---------|

| SIM Card Supplies (VSIM                            | 1, VSIM2)                                                                                            |                 |          |              |         |

| 1.8V Output Voltage                                |                                                                                                      | 1.65            | 1.8      | 1.95         | V       |

| 3.0V Output Voltage                                |                                                                                                      | 2.82            | 3.0      | 3.18         | V       |

| Output Short Current                               |                                                                                                      |                 | 38       |              | mA      |

| Limit                                              |                                                                                                      |                 |          |              |         |

| Load Regulation(1.8V)                              | 0.05mA <i_load<20ma at="" vbat="3.6V&lt;/td"><td></td><td>1</td><td>10</td><td>mV</td></i_load<20ma> |                 | 1        | 10           | mV      |

| Load Regulation(3.0V)                              |                                                                                                      |                 | 1.7      | 10           |         |

| Turn-On Time                                       | No load, Enable to VSIM1,2 at 90%                                                                    |                 | 0.8      | 1.5          | ms      |

|                                                    | selected voltage                                                                                     |                 |          |              |         |

| GSM Interface                                      |                                                                                                      |                 |          |              |         |

| Vih(SIMCLK, SIMRST)                                |                                                                                                      | Vio-0.6         |          |              | V       |

| Vil (SIMCLK, SIMRST)                               |                                                                                                      |                 |          | 0.6          | V       |

| Vil (SIMIO)                                        | Vol<=0.4V, lol=1mA                                                                                   |                 |          | 0.23         | V       |

|                                                    | Vol<=o.4V, Iol=0mA                                                                                   |                 |          | 0.335        |         |

| Vih(SIMIO), Voh(SIMIO)                             | lih,loh= $\pm 20$ uA                                                                                 | Vio-0.6         |          |              | V       |

| lil(SIMIO)                                         | Vil=0V                                                                                               |                 |          | 0.9          | mA      |

| Vo(SIMIO)                                          | Vil=0.4V                                                                                             |                 |          | 0.42         | V       |

| Interface to 3V SIM Card                           |                                                                                                      |                 |          |              |         |

| Vol(SRST)                                          | Sink Current=-20uA (VSIMRST=0.6V)                                                                    |                 |          | 0.4          | V       |

| Voh(SRST)                                          | Source                                                                                               | 0.9*VSIM        |          |              | V       |

|                                                    | Current=200uA(VSIMRST=Vio-0.6V)                                                                      |                 |          |              |         |

| Vol(SCLK)                                          | Sink Current= -20uA (VSIMCLK=0.6V                                                                    |                 |          | 0.4          | V       |

| Voh(SCLK)                                          | Source                                                                                               | 0.9*VSIM        | _        |              | V       |

|                                                    | Current=200uA(VSIMCLK=Vio-0.6V)                                                                      |                 |          |              |         |

| Vil(SIO)                                           |                                                                                                      |                 | <b> </b> | 0.15*VSIM    | V       |

| Vih(SIO), Voh(SIO)                                 | Source Current=20uA                                                                                  | VSIM-0.4        |          |              | V       |

| lil(SIO)                                           | VSIO=0V                                                                                              |                 | <b> </b> | -1           | mA      |

| Vol(SIO)                                           | Sink Current=-1mA(VSIMIO=0V)                                                                         |                 |          | 0.15*VSIM    | V       |

| Interface to 1.8V SIM Car                          |                                                                                                      | Т               | T        |              |         |

| Vol(SRST)                                          | Sink Current=-20uA(VSIMRST=0.6V)                                                                     | 2 211 (211 (    |          | 0.2*VSIM     | V       |

| Voh(SRST)                                          | Source                                                                                               | 0.9*VSIM        |          |              | V       |

| V-1/00LK)                                          | Current=200uA(VSIMRST=Vio-0.6V)                                                                      |                 |          | 0.0*\/0.184  | \ /     |

| Vol(SCLK)                                          | Sink Current= -20uA (VSIMCLK=0.6V                                                                    | 0.0*\/0\\       |          | 0.2*VSIM     | V       |

| Voh(SCLK)                                          | Source                                                                                               | 0.9*VSIM        |          |              | V       |

| Vil(SIO)                                           | Current=200uA(VSIMCLK=Vio-0.6V)                                                                      |                 |          | 0.15*VSIM    | V       |

| Vii(SIO)<br>Vih(SIO), Voh(SIO)                     | Source Current=20uA                                                                                  | VSIM-0.4        |          | 0.15 VSIIVI  | V       |

| lil(SIO)                                           | VSIO=0V                                                                                              | V S II VI - U.4 |          | -1           |         |

| Vol(SIO)                                           | Sink Current=-1mA(VSIMIO=0V)                                                                         |                 |          | 0.15*VSIM    | mA<br>V |

|                                                    |                                                                                                      |                 |          | U. 15 VSIIVI | V       |

| SIM Card Interface Timin SRST, SIO rise/fall times | y VSIM=3, 1.8V, loaded with 30uF                                                                     | T               | 1        | E00          | l no    |

| SRS1, SIO rise/rail times                          | (10%~90%)                                                                                            |                 |          | 500          | ns      |

| SCLK rise/fall times                               | VSIM=3, 1.8V, loaded with 30uF(10%~90%)                                                              |                 |          | 15           | ns      |

| COLIX HSC/Idll tillles                             | VSIM=1.8V, loaded with 30uF                                                                          |                 |          | 40           | ns      |

|                                                    | (10%~90%)                                                                                            |                 |          | +0           | 113     |

| SCLK frequency                                     | (1070 3070)                                                                                          | 5               |          |              | MHz     |

| SCLK frequency                                     | SIMCLK Duty=50%, fSIMCLK=5MHz                                                                        | 47              |          | 53           | %       |

| SCLK duty cycle SCLK propagation delay             | From SIMCLK to SCLK,load with30pF                                                                    | 71              | 8        | 10           | 1       |

| SOLIN propagation delay                            | FIGHT SHVICEN TO SCEN, TOAU WITHSUPF                                                                 |                 | U        | IU           | ns      |

Details of the individual subsystems and blocks are described in following Chapters.

## Serial Port Interface (SPI)

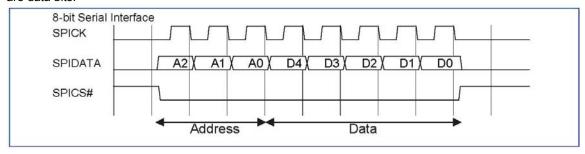

This module is used to receive the commands transmitted by baseband processor. It will decode the received data and send corresponding commands to signal processing and analog blocks. The 8-bit serial interface uses three pins –SPICS#, SPIDATA an SPICK- to enter data. Data read is not available with the serial interface and data entered must be 8 bits. The description of three pins is:

| Signal Name | Attribute      | Direction   | Description       |

|-------------|----------------|-------------|-------------------|

| SPICK       | Edge Triggered | BB->BCT4302 | Serial bus clock  |

| SPIDATA     | Level          | BB->BCT4302 | Serial data       |

| SPICS       | Active Low     | BB->BCT4302 | SPI bus selection |

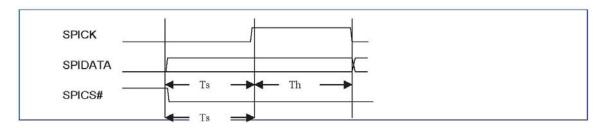

Figure 2 shows the timing diagram of this serial interface. When the block is idle, SPICK is forced LOW and SPICS# is forced HIGH. Once the data register contains data and the interface is enabled, SPICS# is pulled LOW and remains LOW for the duration of the transmission. The first three bits are address bits and the others are data bits.

Figure 2. SPI Interface Transfer Diagram

Figure 3. SPI Interface Timing Diagram

#### **Serial Port Interface Timing**

| Symbol | Parameter                   | Min | Tye | Max | Unit |

|--------|-----------------------------|-----|-----|-----|------|

| Ts     | SPIDATA to SPICK setup time | 4   |     |     | ns   |

| Th     | SPIDATA to SPICK hold time  | 4   |     |     | ns   |

#### **Register Definitions**

## 0000H Reset control Register

| Bit   | 4 | 3      | 2  | 1      | 0  |

|-------|---|--------|----|--------|----|

| Name  |   | RSTVAL |    | RSTSEL |    |

| Туре  |   | WO     | WO | WO     | WO |

| Reset |   | 0      | 0  | 0      | 0  |

The LSB of these two signals is for 1st SIM card, and MSB is for 2nd one.

RSTSEL SIM card RST pin control, only valid when VCCEN is 1.

0 The RST pin of SIM card is the same as BCT4302 input pin SIMRST.

1 The RST pin of SIM card is controlled by RSTVAL as show below.

RSTVAL Control the value of SIM card RST pin, only valid when VCCEN is 1 an RSTSEL is 1.

0 Force the SIM card RST pin to 0.

1 Force the SIM card RST pin to 1.

#### 0001H Clock Control Register

| Bit   | 4 | 3    | 2  | 1    | 0  |

|-------|---|------|----|------|----|

| Name  |   | СРОН |    | CPOL |    |

| Type  |   | WO   | WO | WO   | WO |

| Reset |   | 0    | 0  | 1    | 1  |

The LSB of these two signals is for 1<sup>st</sup> SIM card, and MSB is for 2<sup>nd</sup> one. The value of SIM card pin is controlled by the combination of the two signals when VCCEN is 1.

CPOH, CPOL

- 01 The CLK pin of SIM card is the same as BCT4302 input pin SIMCLK.

- 11 Force the SIM card CLK pin to stop at high.

- 00 Force the SIM card CLK pin to stop at low.

- 10 Not allowed.

#### 0002H Data Control Register

| Bit   | 4 | 3      | 2  | 1      | 0  |

|-------|---|--------|----|--------|----|

| Name  |   | DATA_L |    | DATAEN |    |

| Туре  |   | WO     | WO | WO     | WO |

| Reset |   | 0      | 0  | 0      | 0  |

The LSB of these two signals is for 1<sup>st</sup> SIM card, and MSB is for 2<sup>nd</sup> one.

DATAEN SIM card DATA pin control, only valid when VCCEN is 1.

- The channel between SIM card DATA pin and BCT4302 I/O pin SIMDATA will be gapped. If there were no drivers of these two pins, the they will be pulled high.

- 1 The channel between SIM card DATA pin and BCT4302 I/O pin SIMDATA will be opened. If there Were no drivers of these two pins, then they will be pulled high.

DATA L Control the value of SIM card DATA pin, only valid when both VCCEN and DATAEN are "1"

- 0 normal function.

- 1 Force the SIM card DATA pin to 0.

#### 0003H VCC Control Register

| Bit   | 4 | 3     | 2  | 1    | 0  |

|-------|---|-------|----|------|----|

| Name  |   | VCCEN |    | VSEL |    |

| Type  |   | WO    | WO | WO   | WO |

| Reset |   | 0     | 0  | 0    | 0  |

The LSB of these two signals is for 1<sup>st</sup> SIM card, and MSB is for 2<sup>nd</sup> one.

VCCEN SIM card power control.

- 0 Turn off SIM card VCC pin, all signals to SIM card will be 0.

- Turn on SIM card VCC pin.

VSEL Choose the supply voltage level of SIM card.

- 0 Supply voltage is 1.8V.

- 1 Supply voltage is 3V.

#### 0004H

| Bit   | 4      | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|

| Name  | REFSEL |   |   |   |   |

| Туре  | WO     |   |   |   |   |

| Reset | 0      |   |   |   |   |

**REFSEL** LDO reference selection

0 VIO

1 Bandgap

0005H Bandgap Control Register

| Bit   | 4     | 3      | 2  | 1 | 0 |

|-------|-------|--------|----|---|---|

| Name  | BG_EN | RBGSEL |    |   |   |

| Type  | WO    | WO     | WO |   |   |

| Reset | 0     | 0      | 0  |   |   |

BG EN Embedded bandgap enable

0 Disable

1 Enable

RGBSEL Bandgap T.C. fine turning

00 initial setting

01 minus 1 step

10 plus 1 step

11 plus 2 step

## **Signal Processing Blocks**

The main function of this block is to handle the command ordered by baseband processor about SCLK and SRST. When it receivers commands sent by SPI, it will do the corresponding signal processing, and then sent the results to analog blocks. The commands is transmitted through serial port interface (SPI) and stored in the register set. Signal processing blocks will process signals with corresponding commands. The truth table of SCLK and SRST is shown in the following tables.

| VSIM | СРОН | CPOL | SIMCLK | SCLK        |

|------|------|------|--------|-------------|

| 0    | 0    | 0    | 0      | 0           |

| 0    | 0    | 0    | 1      | 0           |

| 0    | 0    | 1    | 0      | 0           |

| 0    | 0    | 1    | 1      | 0           |

| 0    | 1    | 0    | 0      | 0           |

| 0    | 1    | 0    | 1      | 0           |

| 0    | 1    | 1    | 0      | 0           |

| 0    | 1    | 1    | 1      | 0           |

| 1    | 0    | 0    | 0      | 0           |

| 1    | 0    | 0    | 1      | 0           |

| 1    | 0    | 1    | 0      | 0           |

| 1    | 0    | 1    | 1      | 1           |

| 1    | 1    | 0    | 0      | Not allowed |

| 1    | 1    | 0    | 1      | Not allowed |

| 1    | 1    | 1    | 0      | 1           |

| 1    | 1    | 1    | 1      | 1           |

Table 1. Truth table of SCLK

| VSIM | RSTSEL | RSETVAL | SIMRST | SRST |

|------|--------|---------|--------|------|

| 0    | 0      | 0       | 0      | 0    |

| 0    | 0      | 0       | 1      | 0    |

| 0    | 0      | 1       | 0      | 0    |

| 0    | 0      | 1       | 1      | 0    |

| 0    | 1      | 0       | 0      | 0    |

| 0    | 1      | 0       | 1      | 0    |

| 0    | 1      | 1       | 0      | 0    |

| 0    | 1      | 1       | 1      | 0    |

| 1    | 0      | 0       | 0      | 0    |

| 1    | 0      | 0       | 1      | 1    |

| 1    | 0      | 1       | 0      | 0    |

| 1    | 0      | 1       | 1      | 1    |

| 1    | 1      | 0       | 0      | 0    |

| 1    | 1      | 0       | 1      | 0    |

| 1    | 1      | 1       | 0      | 1    |

| 1    | 1      | 1       | 1      | 1    |

Table 2. Truth table of SRST

It will be noticed that the effect of those controlled signal may not be valid immediately due to the delay of some processing time.

#### **Analog Blocks**

This module contains SIM LDO, level shifter and bandgap function. It will accept the command set by SPI and also transfer the signals to suitable voltage level to SIM cards. The SIM LDO is a regulator that could source 40mA(max) with 1.8V or 3.0V output voltage selection based on the supply specs of subscriber identity modules(SIM) card.

#### **SIM Card Interface**

The SIM card interface circuitry of BCT4302 meets all ETSI and IMT-2000 SIM interface requirements. It provides level shifting needs for low voltage GSM controller to communicate with either 1.8V or 3V SIM cards. All SIM cards contain a clock input, a reset input, and a bi-directional data input/output.

#### **Card Activation and Deactivation**

The role of BCT4302 at card activation and deactivation is just a signal bypasser. It will bypass SIMCLK and SIMRST transmitted by baseband processor and turn on the channel between SIMIO and SIO. When card activation, user just needs to follow the steps listed below.

- ♦ Set VSEL to desired level.

- Turn on VCCEN and DATAEN in sequence, and the other registers just keep their default settings.

- Turn on SIM interface of baseband processor to start activation sequence.

Similarly, when card deactivation, user just follows the steps listed below.

- Turn off SIM interface of baseband processor to start deactivation sequence.

- ♦ Set DATA\_L and then turn off VCCEN, and the other registers just keep their default settings.

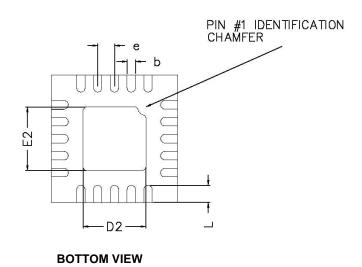

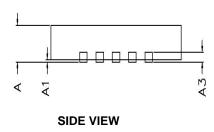

# **Package Information**

| COMMON DIMENSIONS(MM) |                   |                        |      |  |

|-----------------------|-------------------|------------------------|------|--|

| PKG.                  | W: VERY VERY THIN |                        |      |  |

| REF.                  | MIN.              | NOM.                   | MAX  |  |

| Α                     | 0.70              | 0.75                   | 0.80 |  |

| A1                    | 0.00              | 2 <del>1 - 2</del> 5 , | 0.05 |  |

| A3                    |                   | 0.2 REF.               |      |  |

| D                     | 2.95              | 3.00                   | 3.05 |  |

|                       | 2.95              | 3.00                   | 3.05 |  |

| b                     | 0.15              | 0.20                   | 0.25 |  |

|                       | 0.30              | 0.40                   | 0.50 |  |

| D2                    | 1.35              | 1.50                   | 1.60 |  |

| E2                    | 1.35              | 1.50                   | 1.60 |  |

| е                     | 0.40 BSC          |                        |      |  |