# **16-bit Color LED Driver with PWM Control**

### Description

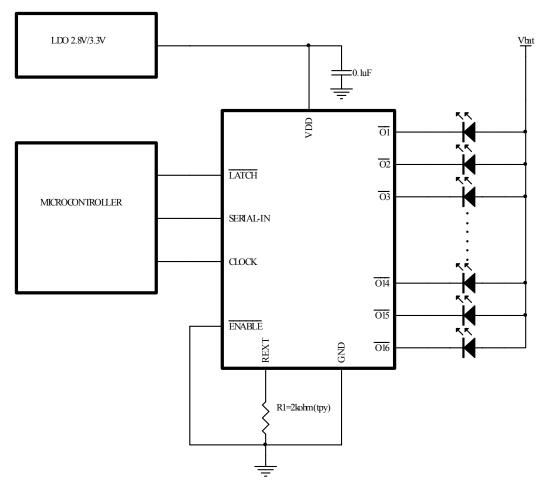

The SN3726 is comprised of constant-current drivers designed for color LEDs. The output current value can be set using an external resistor. The output current value can be adjusted from 5mA to 60mA through the external resistor.

As a result, all outputs will have virtually the same current levels.

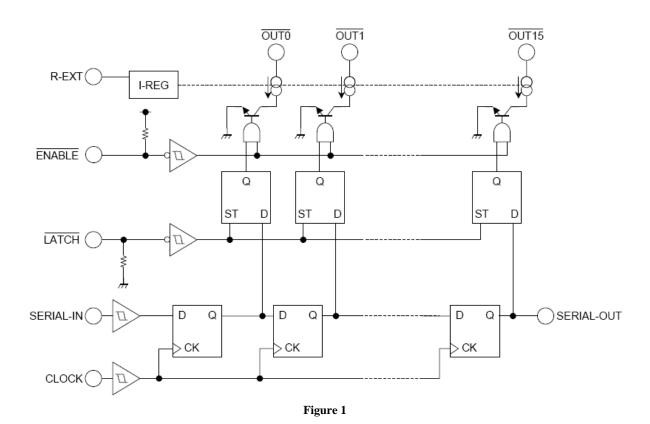

This driver incorporates 16-bit constant t-current outputs, a 16-bit shift register, a 16-bit latch and a 16-bit AND-gate circuit.

These drivers have been designed using the CMOS process.

### Application

- Cellular phones

- MP3/MP4/CD/minidiskplayers

- Toys

#### **Block Diagram**

#### Features

- Output current capability and number of outputs: 60 mA × 16 outputs

- Constant current range: 5 to 60 mA

- Application output voltage:  $\geq 0.4 \text{ V}$

- For anode-common LEDs

- Power supply voltage range  $V_{DD} = 2.7$  to 5.5V

- Serial and parallel data transfer rate: 20 MHz (max, cascade connection)

- Operating temperature range Topr = -40 to  $85^{\circ}$ C

- Package: QFN-24

- Current accuracy (All output ON)

| Output  | Current A    | Output  |            |

|---------|--------------|---------|------------|

| voltage | Between Bits | Current |            |

| ≥0.4V   | $\pm 4\%$    | ±12%    | 5 to 60 mA |

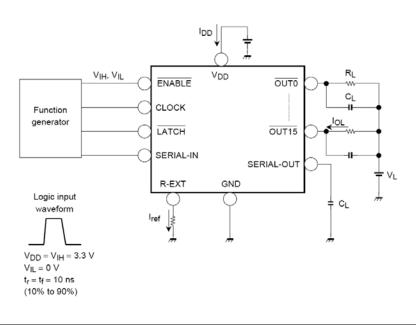

# **Typical Application Circuit**

Figure 2. Typical Application Figure

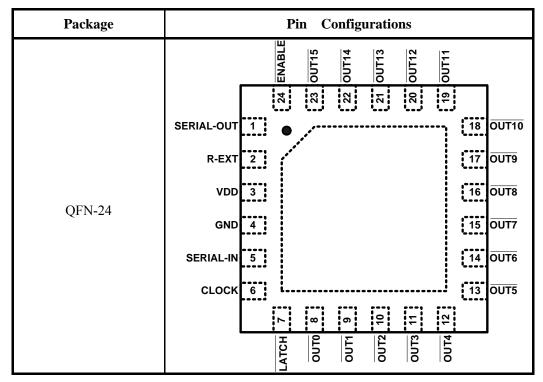

# **Pin Configurations**

# **Pin Description**

| Pin             | Pin No. | I/O | Description                                                                                                                                                                                                            |  |

|-----------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SERIAL-OUT      | 1       | 0   | Output terminal for serial data input on SERIAL-IN terminal                                                                                                                                                            |  |

| R-EXT           | 2       | Ι   | Input terminal used to connect an external resistor.<br>This regulated the output current.                                                                                                                             |  |

| V <sub>DD</sub> | 3       | Ι   | Supply voltage terminal.                                                                                                                                                                                               |  |

| GND             | 4       |     | GND terminal for control logic                                                                                                                                                                                         |  |

| SERIAL-IN       | 5       | Ι   | Input terminal for serial data for data shift register                                                                                                                                                                 |  |

| CLOCK           | 6       | Ι   | Input terminal for clock for data shift on rising edge                                                                                                                                                                 |  |

| LATCH           | 7       | Ι   | Input terminal for data strobe When the $\overrightarrow{LATCH}$ input is driven High data is not latched. When it is pulled Low, data is latched.                                                                     |  |

| OUT0 to OUT15   | 8 to 23 | 0   | Constant-current output terminals                                                                                                                                                                                      |  |

| ENABLE          | 24      | Ι   | Input terminal for output enable.<br>All outputs ( $\overline{OUT0}$ to $\overline{OUT15}$ ) are turned off, when the $\overline{ENABLE}$ terminal is driven High .And are turned on, when the terminal is driven Low. |  |

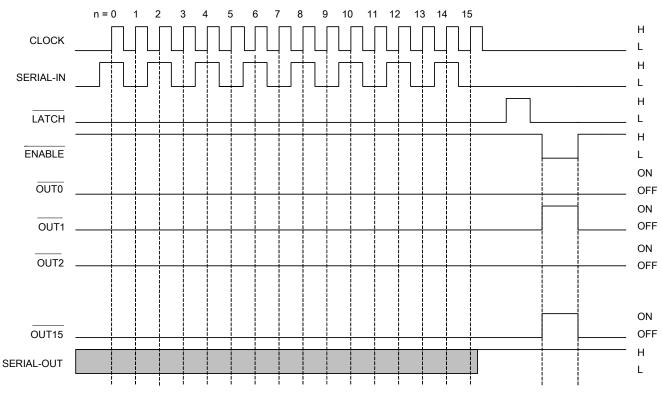

# **Timing Diagram**

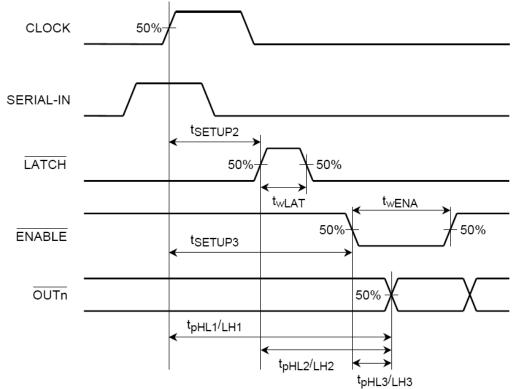

Warning: Latch circuit is leveled-latch circuit. Be careful because it is not triggered-latch circuit.

Note : The latches circuit holds data by pulling the LATCH terminal Low. And, when LATCH terminal is a High level, latch circuit doesn't hold data, and it passes from the input to the output. When  $\overline{ENABLE}$  terminal is a Low level, output terminal  $\overline{OUT0}$  to  $\overline{OUT15}$  respond to the data, and on and off does. And, when  $\overline{ENABLE}$  terminal is a High level, it offs with the output terminal regardless of the data.

# **Truth Table**

| CLOCK    | LATCH | ENABLE | SERIAL-IN | $\overline{\text{OUT0}}$ $\overline{\text{OUT7}}$ $\overline{\text{OUT15}}$ | SERIAL-OUT |

|----------|-------|--------|-----------|-----------------------------------------------------------------------------|------------|

|          | Н     | L      | Dn        | DnDn-7Dn-15                                                                 | Dn-15      |

|          | L     | L      | Dn+1      | No change                                                                   | Dn-14      |

|          | Н     | L      | Dn+2      | Dn+2 Dn-5 Dn-13                                                             | Dn-13      |

| <b>→</b> | Х     | L      | Dn+3      | Dn+2Dn-5Dn-13                                                               | Dn-13      |

| <b>_</b> | Х     | Н      | Dn+3      | OFF                                                                         | Dn-13      |

Note :  $\overline{OUT0}$  to  $\overline{OUT15}$  = On when Dn = H;  $\overline{OUT0}$  to  $\overline{OUT15}$  = Off when Dn = L. In order to ensure that the level of the power supply voltage is correct, an external resistor must be connected between *R*-EXT and *GND*.

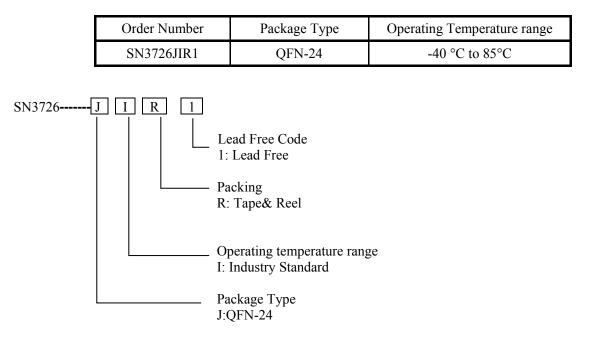

# **Ordering Information**

Storage temperature range,  $T_{stg}$  ----- -55°C to 150°C

# **Absolute Maximum Ratings**

- •

- •

- Operating temperature range, Topr---- -40°C to 85°C •

# **Recommended Operating Conditions**

(Topr =  $40^{\circ}C$  to  $85^{\circ}C$  unless otherwise specified)

| Characteristics                | Symbol              | Conditions                      | Min                  | Тур. | Max                   | Unit  |  |

|--------------------------------|---------------------|---------------------------------|----------------------|------|-----------------------|-------|--|

| Supply voltage                 | V <sub>DD</sub>     |                                 | 2.7                  |      | 5.5                   | V     |  |

| Output voltage                 | V <sub>OUT</sub>    |                                 |                      | 0.7  | 4                     | V     |  |

|                                | I <sub>OUT</sub>    | Each DC 1<br>circuit            | 5                    | _    | 60                    | mA/ch |  |

| Output current                 | I <sub>OH</sub>     | SERIAL-OUT                      |                      |      | -1                    |       |  |

|                                | I <sub>OL</sub>     | SERIAL-OUT                      |                      |      | 1                     | mA    |  |

| • · · •                        | V <sub>IH</sub>     |                                 | 0.7 *V <sub>DD</sub> |      | V <sub>DD</sub> +0.15 | V     |  |

| Input voltage                  | $V_{IL}$            | —                               | -0.15                |      | 0.3*V <sub>DD</sub>   |       |  |

| Clock frequency                | f <sub>CLK</sub>    | Cascade                         |                      |      | 20                    | MHZ   |  |

| LATCH purse width              | t <sub>wLAT</sub>   | connected                       | 50                   |      |                       | ns    |  |

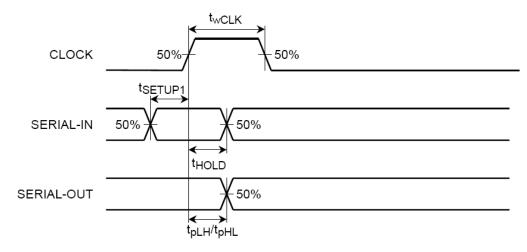

| CLOCK pulse width              | t <sub>wCLK</sub>   | _                               | 25                   |      |                       | ns    |  |

|                                |                     | Upper<br>I <sub>OUT</sub> =20mA | 2000                 | _    | _                     | ns    |  |

| ENABLE pulse width (note)      | t <sub>wENA</sub>   | Lower<br>I <sub>OUT</sub> =20mA | 3000                 |      |                       |       |  |

| Set-up time for CLOCK terminal | t <sub>SETUP1</sub> |                                 | 10                   |      |                       | ns    |  |

| Hold time for CLOCK terminal   | t <sub>HOLD</sub>   | _                               | 10                   |      |                       | ns    |  |

| Set-up time for LATCH terminal | t <sub>SETUP2</sub> |                                 | 50                   |      |                       | ns    |  |

•

Note : When the pulse of the Low level is inputted to the ENABLE terminal held in the High level.

| Characteristics                          | Symbol                | Conditions                                       |                        | Min          | Тур. | Max             | Unit |

|------------------------------------------|-----------------------|--------------------------------------------------|------------------------|--------------|------|-----------------|------|

| Supply voltage                           | V <sub>DD</sub>       | Normal operation                                 |                        | 2.7          |      | 5.5             | V    |

|                                          | I <sub>OUT1</sub>     | V <sub>OUT</sub> =0.4V,<br>V <sub>DD</sub> =3.3V |                        | 17.2         | 18.7 | 20.2            |      |

| Output current                           | I <sub>OUT2</sub>     | $V_{OUT}=0.4V,$<br>$V_{DD}=5V$                   | $R_{EXT}=1K\Omega$     | 17.5         | 18.9 | 20.4            | mA   |

| Output current error between bits        | $\triangle I_{OUT1}$  | V <sub>OUT</sub> ≥0.4V,<br>All outputs ON        | $R_{EXT}=1K\Omega$     | _            | ±3   | ±4              | %    |

| Output leakage current input voltage     | I <sub>OZ</sub>       | V <sub>OUT</sub> =                               | 5.0V                   | —            |      | 1               | uA   |

| <b>.</b>                                 | V <sub>IN</sub>       | _                                                |                        | $0.7 V_{DD}$ | _    | V <sub>DD</sub> |      |

| Input voltage                            |                       |                                                  |                        | GND          |      | $0.3V_{DD}$     | V    |

|                                          | V <sub>OL</sub>       | $I_{OL}$ =1.0mA, $V_{DD}$ =3.3V                  |                        | _            |      | 0.3             |      |

|                                          |                       | $I_{OL}$ =1.0mA, $V_{DD}$ =5V                    |                        | _            |      | 0.3             | V    |

| SOUT terminal voltage                    |                       | I <sub>OH</sub> =-1.0mA,V <sub>DD</sub> =3.3V    |                        | 3            |      | _               |      |

|                                          | V <sub>OH</sub>       | I <sub>OH</sub> =-1.0mA,V <sub>DD</sub> =5V      |                        | 4.7          |      | _               |      |

| Output current supply voltage regulation | %/V <sub>DD</sub>     | When V <sub>DD</sub> is changed 2.7V to 5.5V     |                        | _            | -1   | -5              | %    |

| Pull-up resistor                         | R <sub>(Up)</sub>     | ENABLE terminal                                  |                        |              |      |                 |      |

| Pull-down resistor                       | R <sub>(Down)</sub>   | LATCH terminal                                   |                        | 115          | 230  | 460             | kΩ   |

|                                          | I <sub>DD(OFF)1</sub> | VOUT=5V                                          | R <sub>EXT</sub> =OPEN |              | 0.18 | 0.25            |      |

| Supply current                           | I <sub>DD(OFF)2</sub> | VOUT=5V,<br>All outputs OFF                      | R <sub>EXT</sub> =1KΩ  | 2            | 3.5  | 3.8             | mA   |

|                                          | I <sub>DD(ON)1</sub>  | VOUT=0.7V,<br>All outputs ON                     | $R_{EXT}=1K\Omega$     | _            | 3.5  | 4               |      |

Electrical Characteristics (Topr = 25°C, VDD=2.7V to 5.5 V unless otherwise specified)

| Characteristics                        | Symbol Conditions |                                                                                                                                | Min | Тур. | Max | Unit |

|----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                                        | t <sub>pLH1</sub> | $\frac{\text{CLK- }\overline{\text{OUTn}}}{\text{ENABLE}} = \text{``L''}$                                                      | _   | 80   | 200 |      |

|                                        | t <sub>pLH2</sub> | $\overline{\text{LATCH}} - \overline{\text{OUTn}}$ , $\overline{\text{ENABLE}} = \text{``L''}$                                 | _   | 80   | 200 |      |

|                                        | t <sub>pLH3</sub> | $\overline{\text{ENABLE}}$ - $\overline{\text{OUTn}}$ , $\overline{\text{LATCH}}$ = "H"                                        |     | 130  | 250 |      |

| Propagation delay                      | t <sub>pLH</sub>  | CLK-SERIAL OUT                                                                                                                 | 3   | 5    |     | ns   |

| Tiopagation delay                      | $t_{\rm pHL1}$    | $\frac{\text{CLK-} \overline{\text{OUTn}}}{\overline{\text{ENABLE}} = \text{``L''}},  \overline{\text{LATCH}} = \text{``H''},$ |     | 160  | 250 | 115  |

|                                        | t <sub>pHL2</sub> | LATCH -OUTn , ENABLE="L"                                                                                                       |     | 160  | 250 |      |

|                                        | t <sub>pHL3</sub> | $\overline{\text{ENABLE}}$ - $\overline{\text{OUTn}}$ , $\overline{\text{LATCH}}$ =""H"                                        | _   | 200  | 350 |      |

|                                        | t <sub>pLH</sub>  | CLK-SERIAL OUT                                                                                                                 | 4   | 6    | _   |      |

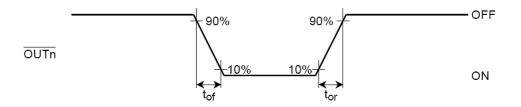

| Output rise time                       | t <sub>or</sub>   | 10~90% of voltage waveform                                                                                                     | 30  | 150  | 200 | ns   |

| Output fall time                       | t <sub>of</sub>   | 90~10% of voltage waveform                                                                                                     | 150 | 200  | 250 | ns   |

| Maximum CLOCK rise time                | t <sub>r</sub>    | When not on DCD (NI-to)                                                                                                        |     |      | 5   | us   |

| Maximum CLOCK fall time t <sub>f</sub> |                   | When not on PCB (Note)                                                                                                         |     |      | 5   | us   |

#### Switching Characteristics (Topr= 25°C unless otherwise specifed)

Conditions: (Refer to test circuit.)

Topr = 25°C,  $V_{DD}=V_{IH}=3.3 V$  and 5 V,  $V_{OUT}=0.7 V$ ,  $V_{IL}=0 V$ ,  $R_{EXT}=1000\Omega$ ,  $V_L=3.0 V$ ,  $R_L=60\Omega$ ,  $C_L=10.5 pF$  Note:

1. If the device is connected in a cascade and tr/tf for the waveform is large, it may not be possible to achieve the timing required for data transfer. Please consider the timings carefully.

2. Delay between outputs. The SN3726 has graduated delay circuits between outputs. The fixed delay time is 5ns (typical), OUT1 has 5ns delay, OUT2 has 10 ns delay, etc. This delay prevents large inrush currents, which reduce power supply bypass capacitor requirements when the outputs turn on. The delay works during switch on and switch off of each output channel. LEDs that have not turned on before ENABLE is low will still turn on and off at the determined delayed time regardless of the state of ENABLE. Therefore, every LED will be illuminated for the amount of time ENABLE is pulled high.

### **Test Circuit**

# **Timing Waveforms**

# 1. CLOCK, SERIAL-IN, SERIAL-OUT

# 2. CLOCK, SERIAL-IN, LATCH, ENABLE, OUTn

3. OUTn

# **Typical Operating Characteristics**

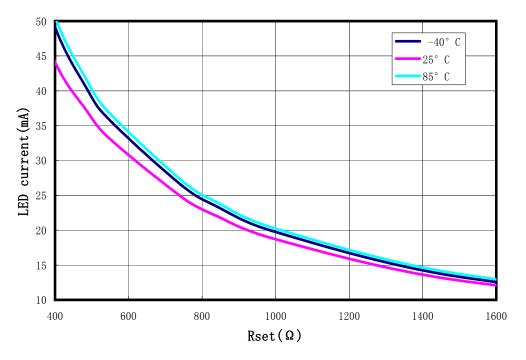

### Adjusting output current

The output current of each channel is set by an external resistor  $R_{ext}$ , the relationship between  $I_{out}$  and  $R_{ext}$  is:  $I_{out} = (V_{R-ext}/R_{ext})^*52$ , the  $V_{R-ext}$  is 0.36V in the SN3726, so we can count the  $I_{out}$  as :  $I_{out} = 0.36^*52/R_{ext}$ . As show in the figure below:

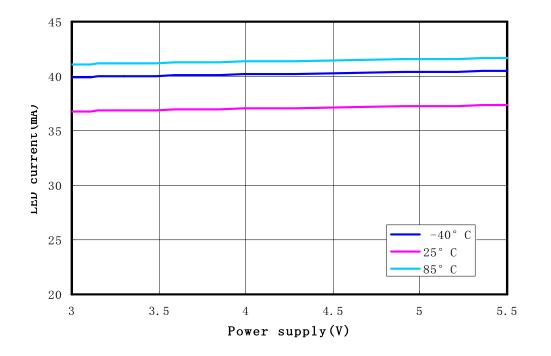

#### **Constant current**

As the figure shown below, the current characteristic of output stage is flat. The output current can be kept constant regardless of the variations of LED forward voltages ( $V_F$ ).this performs as a perfection of load regulation.

10

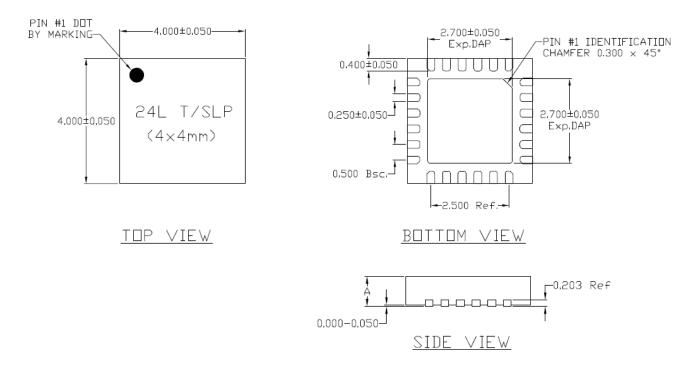

# **Package Information**

| Symbol | Dimension (mm) |      |      |  |  |

|--------|----------------|------|------|--|--|

|        | MIN            | NOM  | MAX  |  |  |

| А      | 0.70           | 0.75 | 0.80 |  |  |

# **RoHS DIRECTIVE COMPLIANCED**

SI-EN Technology certifies that the products and it's packing materials meet the provisions of the RoHS Directive( the restriction of the use of certain hazardous substances in electrical and electronic equipment).

# **RIGHT AND RESTRICTIONS**

SI-EN is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing SI-EN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such SI-EN products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that SI-EN products are used within specified operating ranges as set forth in the most recent SI-EN products specifications.

The SI-EN products listed in this document are designed for usage in general electronics applications, such as electrical appliances, audio-visual equipment, communications devices, personal equipment, office equipment, measuring equipment, industrial robotics and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

SI-EN Technology ,Inc.will not take any responsibilities regarding the misusage of the products mentioned above. Misusing of SI-EN products listed in this document shall be made at the customer's own risk. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. SI-EN Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by SI-EN Technology ,Inc. for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of SI-EN Technology ,Inc. or others.

The information contained herein is subject to change without notice.