# AlazarTech

# **ATS850**

25 MHz, 50 MS/s 8-Bit Waveform Digitizer for PCI Bus

- 2 channels simultaneously sampled at 8-bit resolution

- 50 MS/s real-time sampling rate

- 25 MHz full power bandwidth

- ±20mV to ±20V input range

- Acquisition memory of 256K samples per channel or 16M samples per channel

- API Panel software allows quick start-up without any software development process

- Software Development Kit supports C/C++, VB and LabVIEW

| Product | Bus | Operating<br>System             | Channels | Sampling<br>Rate      | Bandwidth | Memory Per<br>Channel    | Resolution |

|---------|-----|---------------------------------|----------|-----------------------|-----------|--------------------------|------------|

| ATS850  | PCI | Windows 2000/XP<br>Windows 98SE | 2        | 50 MS/s<br>to 10 KS/s | 25 MHz    | 256K Std<br>16M Optional | 8 bits     |

#### **Overview**

ATS850 is a dual-channel 50 MS/s waveform digitizer card for PCI bus. Using an ATS850 low-noise, deepmemory digitizer, you can build faster performance automated test systems at low cost.

ATS850 PCI digitizers are also an ideal solution for cost sensitive OEM applications that require a digitizer to be embedded into the customer's equipment.

More than one ATS850 PCI digitizers can be configured as a Master/Slave system to create a truly simultaneous data acquisition system of up to 16 inputs.

ATS850 is supplied with API Panel software that lets the user get started immediately without having to go through a software development process. Users who need to integrate the ATS850 in their own program can purchase a Windows based software development kit, ATS-SDK for C/C++ and VB or ATS-VI for LabVIEW.

#### **Analog Input**

An ATS850 features two analog input channels with extensive functionality. Each channel has 25 MHz of full power analog input bandwidth. With software selectable attenuation, you can achieve an input voltage range of  $\pm 20$ mV to  $\pm 20$ V. Attenuating probes (sold separately) can extend the voltage range even higher.

Software selectable AC or DC coupling further increases the signal measurement capability. Software selectable  $50\Omega$  input impedance makes it easy to interface to high speed RF signals.

#### **Acquisition System**

ATS850 PCI digitizers use a pair of 50 MS/s, 8-bit ADCs to digitize the input signals. The real-time sampling rate ranges from 50 MS/s down to 10 KS/s. The two channels are guaranteed to be simultaneous, as they share the exact same clock.

An acquisition can consist of multiple records, with each record being captured as a result of one trigger event. Minimum number of records is 1 and maximum is 1000. A record may contain both pre-trigger and post-trigger data.

In between the multiple records being captured, the acquisition system is re-armed by the hardware within 8 sampling clock cycles. This mode of capture, sometimes referred to as Multiple Record or Pre-Trigger Multiple Record, is very useful for capturing data in applications with a very rapid trigger rate.

#### **Acquisition Memory**

The standard ATS850 PCI digitizer features a total of 512KB onboard memory, providing up to 262,140 points of acquisition memory for each channel.

The High Memory version of ATS850 features a total of 32MB of onboard memory, providing 16 Million points of acquisition memory for each channel.

Data is acquired into the onboard memory before being transferred to the host PC memory. This transfer is performed using Direct Memory Access (DMA), which uses scatter-gather bus mastering technology.

### **Triggering**

The ATS850 is equipped with sophisticated triggering options, such as programmable trigger thresholds and slope on any of the input channels or the External Trigger input.

While most oscilloscopes offer only one trigger engine, ATS850 offers two trigger engines (called Engines X and Y). This allows the user to combine the two engines using a logical OR, AND or XOR operand.

Both pre-trigger and post-trigger points can be captured in a given record. The user can specify the number of records to capture in an acquisition, the length of each record and the amount of pre-trigger data. The amount of Post-trigger data can be calculated by subtracting pre-trigger depth from the record length.

A programmable trigger delay can also be set by the user. This is very useful for capturing the signal of interest in a pulse-echo application, such as ultrasound, radar, lidar etc.

## **Trigger Time Stamp**

A 40-bit time stamp counter comes standard with the ATS850. This counter is initialized to a zero value when an acquisition session is started and increments once for every four samples captured, thus providing a 4-clock timing accuracy. The value of this counter is latched into on-board memory for each trigger, i.e. once per record.

This allows the user to find out the timing of each trigger in a multiple record acquisition relative to the start of the acquisition.

#### **Multiple-Digitizer Synchronization**

ATS850 features a Master/Slave connector that allows synchronization of multiple digitizers to allow truly synchronous sampling across as many as 16 channels.

A SyncBoard (sold separately) is required to connect the Master/Slave connectors on multiple digitizers in the system together. Such a system is called a Master/Slave system.

SyncBoard is a board-level product that features controlled impedance, equal length traces to deliver clock, trigger and initialization signals to each ATS850 in the system.

A Master/Slave system is guaranteed to sample simultaneously across all channels in that system. Triggering is also guaranteed to be simultaneous across all digitizers in the system.

ATS850 based master/slave systems provide the best price-performance for high channel count systems.

#### **Optional External Clock**

While the ATS850 features a low jitter, high reliability 50 MHz crystal oscillator as the source of the timebase system, there may be occasions when digitizing has to be synchronized to an external clock source.

ATS850 External Clock option provides a BNC input for a TTL compatible external clock signal with a frequency between 50 MHz and 10 KHz.

This clock signal is terminated on the ATS850 printed circuit board using a  $50\Omega$  resistor. As such, the external clock circuitry must have sufficient drive (± 66mA) to inject the clock signal properly.

The active edge of the external clock is software selectable between the rising or falling edge.

Users can also set a decimation factor for the external clock. For example, if the user wants to digitize the input signal on every tenth clock edge, this factor can be set to 10. Minimum decimation value is 1 and maximum is 100,000.

#### **Calibration**

Every ATS850 digitizer is factory calibrated and is shipped with a calibration certificate verifying that it meets NIST-traceable standards. To recalibrate an ATS850, the digitizer must either be shipped back to the factory or a qualified metrology lab.

#### **Software**

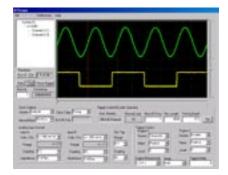

ATS850 is supplied with the API Panel software that allows the user to setup the acquisition hardware and capture, display and archive the signals. With this software, users can get started quickly and effortlessly without going through a software development process.

A Windows compatible software development kit, ATS-SDK is also offered. It allows programs written in C/C++ and VisualBASIC to fully control the ATS850.

A set of high performance VIs for LabVIEW 6.1, called ATS-VI, can also be purchased.

## **Application Programming Interface (API)**

ATS850 features a very simple, high level API, which is designed to make it easy to integrate into an existing program.

ATS850 API does not compromise performance for ease of use. High performance was maintained by designing the hardware-software interface in order to minimize the number of times commands and data have to cross the User-Kernel boundary in the Windows environment.

#### **System Requirements**

Pentium based computer with at least one free PCI slot, 128 MB RAM, 20 MB of free hard disk space, SVGA display adaptor and monitor with at least a  $800 \times 600$  resolution. API Panel software requires Internet Explorer 5.0 or higher.

#### **Power Requirements**

+5V 1.5 A, typical

+5V voltage level must remain between the range of 4.75V to 5.20V at all times after power-on

**Physical**

Size Single slot, half length PCI card

(4.2 inches x 7.2 inches)

Weight 500 g

I/O Connectors

CH A, CH B, EXT, ECLK BNC female connectors

**Environmental**

Operating temperature 0 to 55  $^{\rm 0}$  C Storage temperature -20 to 70  $^{\rm 0}$  C

Relative humidity 5 to 95%, non-condensing

#### **Acquisition System**

Resolution 8 bits

Bandwidth (-3dB)

$\begin{array}{lll} \text{DC-coupled, } 1\text{M}\Omega & \text{DC - 25 MHz} \\ \text{DC-coupled, } 50\Omega & \text{DC - 25 MHz} \\ \text{AC-coupled, } 1\text{M}\Omega & \text{10 Hz - 25 MHz} \\ \text{AC-coupled, } 50\Omega & \text{100KHz - 25 MHz} \\ \end{array}$

Bandwidth flatness:  $\pm 1dB$

Number of channels 2, simultaneously sampled

Maximum Sample Rate 50 MS/s single shot Minimum Sample Rate 10 KS/s single shot

Full Scale Input ranges  $\pm 20$ mV,  $\pm 40$ mV,  $\pm 50$ mV,  $\pm 80$ mV,  $\pm 100$ mV,  $\pm 200$ mV,  $\pm 400$ mV,

±100mV, ±200mV, ±400mV, ±500mV, ±800mV, ±1V, ±2V, ±4V, ±5V, ±8V, ±10V and ±20V,

software selectable.

Exceeding the full scale input range by more than 100% may result in signal distortion due to phase reversal of amplifier stage.

DC accuracy ±2% of full scale in all input

ranges

Input coupling AC or DC, software selectable Input impedance  $50\Omega$  or  $1M\Omega \pm 1\%$  in parallel with

30 pF  $\pm$ 10pF, software selectable

Input protection

$\pm$ 28V (DC + peak AC for CH A,

CH B and EXT only without exter-

nal attenuation)

$\pm$ 8V (DC + peak AC for CH A,

CH B and EXT only without exter-

nal attenuation)

#### **Acquisition Memory System**

Onboard acquisition memory 512 KB standard, or

32MB with High Memory Option

Acquisition Memory/channel Up to 262,140 samples per

channel standard, or Up to 16 Million samples per channel with High Memory Option

Record Length Software selectable with 4 point

resolution. Record length must be a minimum of 256 points. Maximum record length is limited by the acquisition memory per

channel.

Number of Records Software selectable from a

minimum of 1 to a maximum of 1,000 or (Acquisition Memory Per Channel / (Record Length+4)),

whichever is lower

Pre-trigger depth 0 to (Record Length-64), software

selectable with 4 point resolution

Post-trigger depth Record Length - Pre-trigger depth

#### **Timebase System**

Timebase options Internal Clock or

External Clock (Optional)

Internal Sample Rates 50 MS/s, 25 MS/s, 10 MS/s,

5 MS/s, 2 MS/s, 1 MS/s, 500 KS/s, 200 KS/s, 100 KS/s, 50 KS/s, 20KS/s, 10KS/s

Internal Clock accuracy ±100 ppm

## **Dynamic Parameters**

Typical values measured using a randomly selected ATS850 in  $\pm 1V$  input range, DC coupling and  $50\Omega$  impedance. Input was provided by a HP8656A signal genarator, followed by a 9-pole, 5 MHz low-pass filter. Input frequency was set at 4 MHz and amplitude was 650 mV rms (92% of full scale input).

SNR

42 dB

SINAD

40 dB

THD

-46 dB

SFDR

-45 dB

Note that these dynamic parameters may vary from one unit to another, with input frequency and with the full scale input range selected.

#### Optional ECLK (External Clock) Input

Signal Level TTL levels. Compatible with both

3.3V and 5V TTL

$\begin{array}{ll} \text{Input impedance} & 50\Omega \\ \\ \text{Input current requirement} & \pm 66\text{mA} \\ \end{array}$

Maximum frequency 50 MHz with 50%  $\pm$ 5% duty

cvcle

Minimum frequency 10 KHz with 50% ±5% duty cycle

Decimation factor Software selectable from 1 to

100,000

Sampling Edge Rising or Falling,

software selectable

#### **Triggering System**

Mode Edge triggering with fixed hyster-

esis

Number of Trigger Engines 2

Trigger Engine Combination OR, AND, XOR, software select-

able

Trigger Engine Source CH A, CH B, EXT, Software or

None, independently software selectable for each of the two

**Trigger Engines**

Hysteresis  $\pm 5\%$  of full scale input, typical

Trigger sensitivity ±10% of full scale input range.

This implies that the trigger system may not trigger reliably if the input has an amplitude less than ±10% of full scale input range

selected

Trigger level accuracy  $\pm 5\%$ , typical, of full scale input

range of the selected trigger

source

Bandwidth 25 MHz

Trigger Delay Software selectable from 0 to

9,999,999 sampling clock cycles

Trigger Timeout Software selectable with a 10 us resolution. Maximum settable

value is 3,600 seconds. Can also be disabled to wait indefinitely for

a trigger event

#### **EXT (External Trigger) Input**

Input impedance  $1~\text{M}\Omega$  in parallel with 30pF  $\pm 10\text{pF}$

Bandwidth (-3dB)

DC-coupled DC - 25 MHz

AC-coupled 10 Hz - 25 MHz

Input range  $\pm 5V$  or  $\pm 1V$ , software selectable

DC accuracy  $\pm 10\%$  of full scale input Input protection  $\pm 28V$  (DC + peak AC without

external attenuation)

Coupling AC or DC, software selectable

#### **Certification and Compliances**

CE Mark Compliance

All specifications are subject to change without notice

## **ORDERING INFORMATION**

| ATS850-256K (Standard)                                      | ATS850-001 |

|-------------------------------------------------------------|------------|

| ATS850-16M (High Memory)                                    | ATS850-002 |

| ATS850: High Memory Option (only available for ATS850-256K) | ATS850-003 |

| ATS850: External Clock Option                               | ATS850-004 |

| ATS850: SyncBoard 2X                                        | ATS850-005 |

| ATS850: SyncBoard 4X                                        | ATS850-006 |

| ATS850: SyncBoard 8X                                        | ATS850-007 |

| C/C++, VB SDK for ATS850                                    | ATS850-SDK |

| LabVIEW VI for ATS850                                       | ATS850-VI  |

# SOFTWARE DEVELOPMENT FOR OEM APPLICATIONS

The ATS850 was designed with the needs of OEM customers in mind. These customers build capital equipment that has to incorporate an embedded waveform digitizer to handle high speed analog signals output by various sensors in the rest of the machine.

One of the major concerns of OEMs buying a waveform digitizer, as opposed to building it themselves, is the ease of integration of the digitizer in their existing software.

The design team of the ATS850 was able to draw upon decades of experience in the industry to formulate software development kits (SDKs) for C/C++, VB and LabVIEW that minimize integration time, without compromising data transfer speed.

One of the most important parts of the SDK is the API Panel software. This is a Win32 application program that uses the same API calls as the SDK to setup the hardware, capture data and then display it. Raw data can also be saved to an ASCII file for easy import into Excel, MATLAB etc.

Software developers can compare the data captured under their program control against that captured by API Panel software to verify that their program works properly.

The ease of software development can also be taken advantage of by non-OEM customers. ATS850 can be integrated into customers' test systems just as easily as in OEM systems.

#### Manufactured By:

#### AlazarTech

3539 ST-CHARLES, SUITE 640 MONTREAL, QC, CANADA H9H 3C4

TEL: (514) 633-0001 FAX: (514) 633-0021

E-MAIL: info@alazartech.com