浅谈神经网络在FPGA平台上的实现方案

出处:电子发烧友网 发布于:2018-10-17 14:30:19

近十年来,人工智能又到了一个快速发展的阶段。深度学习在其发展中起到了中流砥柱的作用,尽管拥有强大的模拟预测能力,深度学习还面临着超大计算量的问题。在硬件层面上,GPU,ASIC,FPGA都是解决庞大计算量的方案。本文将阐释深度学习和FPGA各自的结构特点以及为什么用FPGA加速深度学习是有效的,并且将介绍一种递归神经网络(RNN)在FPGA平台上的实现方案。

揭开深度学习的面纱

深度学习是机器学习的一个领域,都属于人工智能的范畴。深度学习主要研究的是人工神经网络的算法、理论、应用。自从2006年Hinton等人提出来之后,深度学习高速发展,在自然语言处理、图像处理、语音处理等领域都取得了非凡的成就,受到了巨大的关注。在互联网概念被人们普遍关注的时代,深度学习给人工智能带来的影响是巨大的,人们会为它隐含的巨大潜能以及广泛的应用价值感到不可思议。

事实上,人工智能是上世纪就提出来的概念。1957年,Rosenblatt提出了感知机模型(Perception),即两层的线性网络;1986年,Rumelhart等人提出了后向传播算法(Back PropagaTIon),用于三层的神经网络的训练,使得训练优化参数庞大的神经网络成为可能;1995年,Vapnik等人发明了支持向量机(Support Vector Machines),在分类问题中展现了其强大的能力。以上都是人工智能历史上比较有代表性的事件,然而受限于当时计算能力,AI总是在一段高光之后便要陷入灰暗时光——称为:“AI寒冬”。

然而,随着计算机硬件能力和存储能力的提升,加上庞大的数据集,现在正是人AI发展的时机。自Hinton提出DBN(深度置信网络)以来,人工智能就在不断的高速发展。在图像处理领域,CNN(卷积神经网络)发挥了不可替代的作用,在语音识别领域,RNN(递归神经网络)也表现的可圈可点。而科技巨头也在加紧自己的脚步,谷歌的领军人物是Hinton,其重头戏是Google brain,并且在去年还收购了利用AI在游戏中击败人类的DeepMind;Facebook的领军人物是Yann LeCun,另外还组建了Facebook的AI实验室,Deepface在人脸识别的准确率更达到了惊人的97.35%;而国内的巨头当属百度,在挖来了斯坦福大学教授Andrew Ng(Coursera的联合创始人)并成立了百度大脑项目之后,百度在语音识别领域的表现一直十分强势。

一览深度学习

简单来说,深度学习与传统的机器学习算法的分类是一致的,主要分为监督学习(supervised learning)和非监督学习(unsupervised learning)。所谓监督学习,就是输出是有标记的学习,让模型通过训练,迭代收敛到目标值;而非监督学习不需要人为输入标签,模型通过学习发现数据的结构特征。比较常见的监督学习方法有逻辑回归、多层感知机、卷积神经网络登;而非监督学习主要有稀疏编码器、受限玻尔兹曼机、深度置信网络等。所有的这些都是通过神经网络来实现的,他们通常来说都是非常复杂的结构,需要学习的参数也非常多。但是神经网络也可以做简单的事情,比如XNOR门,如图。

在图1(a)中,两个输入x_1和x_2都是分别由一个神经元表示,在输入中还加入了一个作为偏置(bias)的神经元,通过训练学习参数,终整个模型的参数收敛,功能和图1(b)真值表一模一样。图1(c)分类结果。

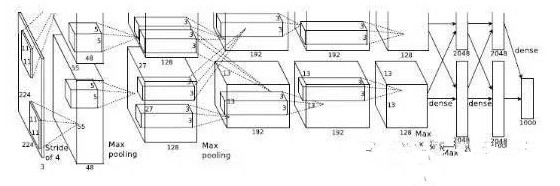

而通常来说,模型都是比较复杂的。比如ILSVRC2012年图像识别大赛中Krizhevsky等人构建出来的 Alex Net。他们一共构建了11层的神经网络(5个卷积层,3个全连接层,3个池化层),一共有65万个神经元,6千万个参数,终达到了15.2%的识别错误率,大大于第二名的26.2%。

当前深度学习得以流行,是得益于大数据和计算性能的提升。但其仍然遭受计算能力和数据量的瓶颈。针对数据量的需求,们可以通过模型的调整、变更来缓解,但计算力的挑战没有捷径。科大讯飞、百度、阿里、360在深度学习方面也面临着计算力的困扰。科大讯飞的深度学习平台属于计算密集型的平台,集群几百台机器之间要实现高速互联,是类似超算的结构,但它又不是一个非常典型的超算。科大讯飞开始探索传统的方式,用大量CPU来支持大规模数据预处理,运行GMM-HMM等经典模型的训练,在千小时的数据量下,效果很不好。而360每天处理的数据有上亿条,参数50万以上,如果用CPU,每次模型训练就要花几天,这对于崇尚快速迭代的互联网公司运营来说简直是不可接受的。

为什么选择FPGA

FPGA(Field Programmable Gate Array)是在PAL、GAL、CPLD等可编程逻辑器件的基础上进一步发展的产物。它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了全定制电路的不足,又克服了原有可编程逻辑器件门电路数有限的缺点。FPGA的开发相对于传统PC、单片机的开发有很大不同。FPGA以并行运算为主,以硬件描述语言来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别。FPGA开发需要从顶层设计、模块分层、逻辑实现、软硬件调试等多方面着手。FPGA可以通过烧写位流文件对其进行反复编程,目前,绝大多数 FPGA 都采用基于 SRAM(StaTIc Random Access Memory 静态随机存储器)工艺的查找表结构,通过烧写位流文件改变查找表内容实现配置。

使用CPU。在2006年的时候,人们还是用串行处理器处理机器学习的问题,当时Mutch 和 Lowe开发了一个工具FHLib(feature hierarchy library)用来处理hierarchical 模型。对于CPU来说,它所要求的编程量是比较少的并且有可迁移性的好处,但是串行处理的特点变成了它在深度学习领域的缺点,而这个缺点是致命的。时至今日,据2006年已经过去了十年,过去的十年集成电路的发展还是遵循着摩尔定律,CPU的性能得到了极大的提升,然而,这并没有让CPU再次走入深度学习研究者的视野。尽管在小数据集上CPU能有一定的计算能力表现,多核使得它能够并行处理,然而这对深度学习来说还是远远不够的。

使用GPU。GPU走进了研究者的视线,相比于CPU,GPU的数大大提高了,这也让它有更强大的并行处理能力,它还有更加强大的控制数据流和储存数据的能力。Chikkerur进行了CPU和GPU在处理目标识别能力上的差别,终GPU的处理速度是CPU的3-10倍。

使用ASIC。专用集成电路芯片(ASIC)由于其定制化的特点,是一种比GPU更高效的方法。但是其定制化也决定了它的可迁移性低,一旦专用于一个设计好的系统中,要迁移到其它的系统是不可能的。并且,其造价高昂,生产周期长,使得它在目前的研究中是不被考虑的。当然,其优越的性能还是能在一些领域胜任。用的就是ASIC 的方案,在640×480pixel的图像中识别速率能达到 60帧/秒。

使用FPGA。FPGA在GPU和ASIC中取得了权衡,很好的兼顾了处理速度和控制能力。一方面,FPGA是可编程重构的硬件,因此相比GPU有更强大的可调控能力;另一方面,与日增长的门资源和内存带宽使得它有更大的设计空间。更方便的是,FPGA还省去了ASIC方案中所需要的流片过程。FPGA的一个缺点是其要求使用者能使用硬件描述语言对其进行编程。但是,已经有科技公司和研究机构开发了更加容易使用的语言比如Impulse Accelerated Technologies Inc. 开发了C-to-FPGA编译器使得FPGA更加贴合用户的使用,耶鲁的E-Lab 开发了Lua脚本语言。这些工具在一定程度上缩短了研究者的开发时限,使研究更加简单易行。

在FPGA上运行LSTM神经网络

LSTM简介

传统的RNN由一个三层的网络:输入层it,隐藏层ht,输出层yt;其中ht的信息作用到下一时刻的输入,这样的结构简单的模仿了人脑的记忆功能,图3是其拓扑图:

只有一个隐藏层方程:

其中 Wx和 Wh分别是输入和隐藏层的权重,b 是偏置。

LSTM 是RNN(递归神经网络)的一种,在处理时序数据得到了广泛的应用,它由门控制信息一共有三个个门:输入门it,遗忘门ft,输出门ot,另外还有隐藏层ht和记忆细胞ct。图4是其拓扑图:

输入门控制了某一时刻的输入;遗忘门通过作用到上一时刻记忆细胞上,控制了上一时刻的数据流要流多少进入下一时刻;记忆细胞是由上一时刻的输入和这一时刻的候选输入共同决定的;输出门作用到记忆细胞上,决定了这一时刻的隐藏层信息,并且送到下一层神经网络上。全部方程如下:

其中W 代表各自的权重,b 代表各自的偏置, σ 是logisTIc sigmoid 函数:

设计FPGA模块

一种递归神经网络在FPGA平台上的实现方案详解

LSTM主要进行的是矩阵的乘法和非线性函数的计算(tanh,sigmoid),因此,选择了Q8.8定点。

矩阵乘法由MAC单元进行(MulTIply Accumulate),一共有两个数据流:向量和权重矩阵流,如图6(a)。在迭代完之后MAC就会重置以防止之前的数据混入下一时刻的数据。两个MAC单元的数据相加之后进行非线性函数计算。同时用一个rescale模块将32位的数据转变为16位的数据。

标量计算的模块,是为了计算ct和ht,终传入下一时刻的计算。如图6(b)。

整个模型一共用了三个图6(a)和一个图6(b)的模块,如图6(c)。数据的流入流出用了DMA(Direct Memory Access)串口控制。由于DMA串口是独立的,因此,还需要一个时钟模块对其进行时序控制。时钟模块主要是一个缓冲存储器组成并暂存了一些数据直到数据都到达。当的一个端口数据流入时钟模块才开始传送数据,这保证了输入跟权重矩阵是同个时刻相关的。

通过在不同平台上训练LSTM网络,我们得到了不同模型的对比。表1是平台的参数,运行结果如图7,可以发现:即使在142MHz的时钟频率下,FPGA平台下的运行时间远远小于其他平台,并行八个LSTM 记忆细胞的处理取得了比 Exynos5422 快16倍的结果。

深度学习采用包含多个隐藏层的深层神经网络(DeepNeural Networks,DNN)模型。DNN内在的并行性,使得具备大规模并行体系结构的GPU和FPGA成为加速深度学习的主流硬件平台,其突出优势是能够根据应用的特征来定制计算和存储结构,达到硬件结构与深度学习算法的匹配,获得更高的性能功耗比;并且,FPGA灵活的重构功能也方便了算法的微调和优化,能够大大缩短开发周期。毫无疑问,FPGA在深度学习的未来是十分值得期待的。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 网桥是什么_网桥如何设置2024/4/12 17:39:56

- TEC 控制器在电信系统中的应用指南2024/4/8 17:43:07

- 什么是5G NR技术?2024/4/8 17:31:58

- OFDMA基本原理2024/4/7 17:45:04

- 一文读懂3GPP到底是什么2024/4/1 17:46:30