FPGA电源设计有哪些规范设计

出处:与非网 发布于:2021-07-07 14:49:50

作为一种复杂的集成电路,FPGA 系统供电的电源的设计与一般的电子系统相比,要求也更高,需要具备高 、高密度、可控性、高效及小型化等的特点。本文系统介绍了 FPGA 电源的不同特性,同时会通过实例,让工程师更深入地了解各特性的意义,以及 FPGA 规范约束及其对电源设计的影响,以便快速完成 FPGA 系统的电源设计。

前言

FPGA (Field Programmable Gate Arrays) 是现今 复杂的集成电路之一。它们采用先进的晶体管技术和芯片架构实现高性能、小体积的高端产品,而为 FPGA 系统供电的电源与一般的电子系统相比,要求更高。

随着市场上对 FPGA 系统应用的普及,对其电源解决方案的需求也越来越旺盛,FPGA 电源系统除了需要满足基本要求外,还需要具备高 、高密度、可控性、高效及小型化等的特点。

现实中,工程师希望将大部分时间花在编程上,而不想花太多的时间和精力考虑如何设计合适的电源耗材。所以在本文中,我们会介绍 FPGA 电源的不同特性,同时会通过实例,让工程师更深入地了解各特性的意义,以及 FPGA 规范约束及其对电源设计的影响。

电压

内核电源电压 (Core Power Supply) 是平衡 FPGA 功耗和性能的 重要关键要素之一。规格书中一般会列出可接受的电压范围,但此范围并不是完整的描述,对 FPGA 而言,电源电压在满足线路运作要求的同时,也需要权衡和优化。下图一是以 Intel 的 Arria 10 FPGA 内核电压要求为例,其也代表了其他 FPGA 内核的电压要求。一般会显示容差范围额定电压,例如 Arria 10 FPGA 为±0.03V,FPGA 会在这个电压窗口内运行得很好,但实际情况比图片显示复杂很多。

事实上,FPGA 可以在不同电压下工作,这具体取决于其特殊的制造公差以及所采用的特定逻辑设计。即使是同一电压要求,一个 FPGA 所需的静态电压也可能是与另一个 FPGA 不同,所以在电源设计时必须要考虑对应 FPGA 的动态与静态之间的变化而自行调控。

动态功率和静态功率

设计合适的 FPGA 电源方案,目标是产生恰当的性能水平来操作编程功能,减少不必要的功耗。我们从半导体物理学的角度看,动态和静态功率都随着内核 VDD 的增加而显著增加,因此我们的目标是让 FPGA 有足够电压来正常运行,以满足其时间要求——因为过量功耗不但对提高性能没有任何帮助,相反它会令晶体管漏电流随着温度的升温,消耗更多的不必要的电力。由于这些原因,当务之急是优化设计和工作点的电压。

该优化过程需要非常 的电源才能获得成功。如果内核电压低于要求,则 FPGA 可能由于时序错误而发生故障。如果内核电压漂移超过 大规格,可能会损坏 FPGA,或者可能会在逻辑中产生保持时间故障。所以,必须考虑电源容差范围来防止所有这些情况,并且仅保证保持在规格限制内的指令电压。

问题是大多数电源调节器都不够准确。调节电压可以在被指令电压附近的公差范围内的任何地方,并且它可以随负载条件、温度和老化而漂移。±2%容差的电源即表示可以在 4%的电压范围内输出任何值。为了补偿电压处于 2%过低的可能性,被指令电压必须比满足时序所需的电压提高 2%。如果经过调节器后电压漂移到高于被指令电压 2%处,它将比该工作点所需的 小电压运行高 4%。这仍然符合规定的 FPGA 所需的电压要求,却浪费了大量功率。

解决这一问题的方案是选择能够以更严格的电压容差运行的电源调节器。使用具有±0.5%容差的调节器,可以在所需的工作频率下、更接近所需的 小规格内工作,并且保证与所需的电压相差小于 1%。这样,好让 FPGA 在 小功耗的情况下,正常工作。

高电量需求

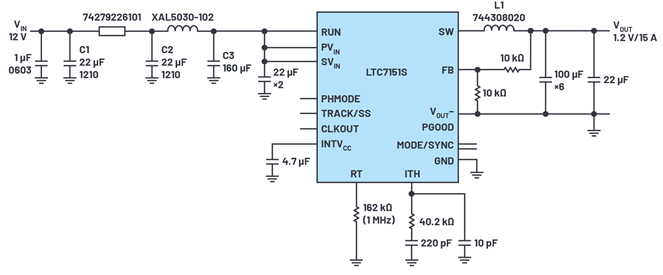

FPGA 系统中的器件通常需要不同调节电压,例如电压的内核电压处理器,其要求电压可以是 0.8V、1.0V、1.2V、1.5V 或 1.8V 等。虽然是低电压供应,但其密集的晶体管结构及长期保持高速运作的情况下,供电电源方案可能需要 10A 或以上,具体的处理器要求通常决定了其他电源要求,例如负载瞬态恢复、待机模式等,这需要负载点(Point-of-Load,或简称 PoL)稳压电源专为 电压设计。 PoL 稳压电源是一种高性能稳压器,其各 Vout 电压轨独立于各自的负载设置。这有助于解决高瞬态电流的要求以及诸如 FPGA 高性能半导体器件的低噪声要求。例如 ADI 公司的 LTM4678 系列,包含两组能够同时提供高密度的电源供应输出。

可控性需求

FPGA 中含有大量而复杂编排的晶体管,一块芯片包含数亿个晶体管,当中被分割成可以设计并独立管理的内核段、模块段和隔断。这些特定的编排是的其具有许多不同电源域,在电压、电流、纹波和噪声以外,还包括启动、关断和故障条件期间的序列顺序,故可控性的 FPGA 电源需要妥善管理输出的次序及其电量

上一篇:反激式开关电源的设计思路

下一篇:在电源设计中如何选择电源模块

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 使用 GaN IC 离线电源的大容量电容器优化2024/4/24 17:30:57

- 并联电压电池2024/4/23 17:45:00

- 运算放大器压摆率和上升时间解释2024/4/22 16:16:53

- B 类放大器的组成及其特性概述2024/4/16 17:22:23

- GaN 基高频 LLC 谐振转换器的设计注意事项2024/4/15 17:21:58