用于多时钟域 SoC 和 FPGA 的同步器技术

出处:维库电子市场网 发布于:2023-02-21 16:55:07

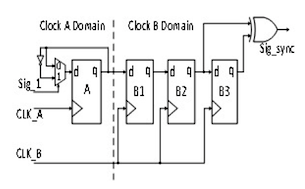

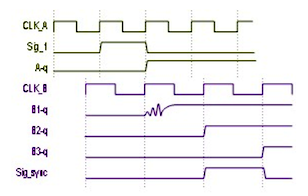

通常,传统的双触发器同步器用于同步单比特电平信号。如图1和图2所示,触发器A和B1工作在异步时钟域。CLK_B 时钟域中的触发器 B1 对输入 B1-d 进行采样时,输出 B1-q 有可能进入亚稳态。但在 CLK_B 时钟的一个时钟周期期间,输出 B1-q 可能稳定到某个稳定值。如果 B1 在一个时钟周期内没有稳定到稳定值,则触发器 B2 的输出可以进入亚稳态,但是 B2 在一个完整的目标时钟周期内处于亚稳态的概率非常接近于零。

如果频率太高,可以使用更多数量的触发器级,因为这将有助于降低同步器输出保持在亚稳态的可能性。

传统的 2FF 同步器。

传统 2FF 同步器的定时。

切换同步器

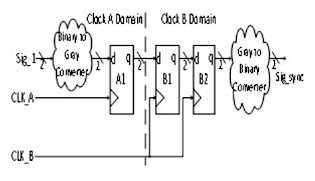

切换同步器用于将源时钟域中生成的脉冲同步到目标时钟域。不能使用 2 FF 同步器直接同步脉冲。使用 2 FF 同步器从快速时钟域同步到慢速时钟域时,可能会跳过脉冲,这会导致脉冲检测丢失,因此依赖于它的后续电路可能无法正常运行。图 3和图 4中的图表显示了切换同步器的实现和时序图。

切换同步器。

切换同步器的时序。

基于握手的脉冲同步器

在基于握手的脉冲同步器中,如图 5和图 6所示,通过提供确认来保证生成到源时钟域的脉冲同步到目标时钟域。脉冲同步器有一个限制,即无法处理背对背(一个时钟间隙)脉冲。为了确保源时钟域中下一个生成的脉冲在目标时钟域中得到明确传输和同步,基于握手的脉冲同步器通过对 A1 和 A3 触发器输出进行“或”运算来生成“忙”信号。因此,产生脉冲的逻辑将不会产生另一个脉冲,直到 busy 信号被断言。

基于握手的脉冲同步器

基于握手的脉冲同步器的定时。

多比特信号的格雷编码当多位信号与 2 触发器同步器同步时,每个位都使用单独的 2-FF 同步器进行同步。亚稳态会导致触发器稳定为真值或假值。所以每个同步器的输出可能不会在同一时钟稳定到正确的值。这会导致数据不一致。为了使用 2 触发器同步器方法同步多位信号,必须保证在特定时钟周期内仅发生单个位变化。这可以通过格雷编码来实现。因此,例如,在异步FIFO设计中,当我们使用2-FF同步器在写时钟域中同步转换为灰度值后的读指针值时,存在亚稳态的可能性。由于格雷编码只有一位变化,所以即使时钟交叉时存在亚稳态,灰色计数器值将是以前的值。例如,读指针(灰度计数器)值从 0110 变为 0111 并与写时钟同步,然后由于亚稳态(如果发生)可能性是读指针仍然保持 0110。现在,假设较早的 FIFO 满标志在读灰度时为高计数器值为 0110,然后 FIFO Full 将在 1 个时钟周期内保持高电平,但这不会导致问题,因为在下一个时钟周期中,读指针值将变为 0111,并且 FIFO 满标志将被置为无效。如果通过两个触发器同步器将二进制计数器从一个时钟域取到另一个时钟域而不是灰色计数器,则多位更改可能会导致亚稳态后不同位的意外恢复(例如,值从“1001”变为“1010”)。图 7和图 8显示了二进制到灰色的转换如何帮助解决这个问题。

多位信号的格雷编码。

多位信号的格雷编码时序。

再循环多路复用同步

对于隔离数据和多个位可以同时传输的情况,使用图 9和图 10中所示的再循环多路复用同步技术。为了同步数据,当数据在源触发器处可用时,在源时钟域中生成控制脉冲。然后根据源域和目标域之间的时钟比率,使用 2 个触发器同步器或脉冲同步器(切换或握手)同步控制脉冲。同步控制脉冲用于在目标域中对总线上的数据进行采样。在目标时钟域中对其进行采样之前,数据应该是稳定的。

再循环多路复用器同步器。

再循环多路复用器同步器的定时。

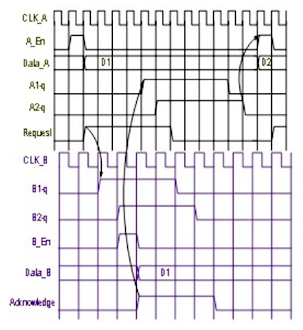

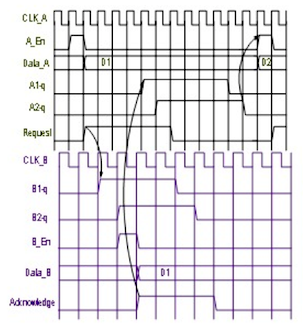

握手同步在这种同步方案中,请求和确认机制用于保证将正确的数据采样到目标时钟域中,而不管源时钟和目标时钟之间的时钟比如何。该技术主要用于同步不连续或不频繁变化的矢量信号。如图 12所示,数据应在总线上保持稳定,直到从目标端接收到同步确认信号 (A2-q) 并且 (A2-q) 变低。图 11中的图表显示了此实现,图 12显示了握手同步器的时序。

握手同步器。

握手同步器的时序。

异步 FIFO 同步

FIFO 是在两个异步时钟域之间同步不断变化的矢量数据的方式。异步 FIFO 同步器提供跨时钟域传输矢量信号的解决方案,而不会有亚稳态和相干性问题的风险。

在异步 FIFO 设计中,FIFO 提供独立于时钟频率的完全同步。如图13所示,经过二进制转灰度后,读写指针分别同步到写时钟域和读时钟域。

先进先出同步器。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 差分传输中的共模噪声:特征和原因2024/4/25 16:15:44

- 毫米波通信技术之香农和香农定理2024/4/24 17:40:43

- 网桥是什么_网桥如何设置2024/4/12 17:39:56

- TEC 控制器在电信系统中的应用指南2024/4/8 17:43:07

- 什么是5G NR技术?2024/4/8 17:31:58