设计和制造超低功耗 MDLL

出处:网络整理 发布于:2024-07-25 16:57:30

但是,这些设备通常需要额外的频率源用于数字和数据传输部分。这包括但不限于 MCU、DSP、FPGA 和 ASIC。很快,您将使用大量晶体和大量 PC 板空间。任何可以将这些时钟连接在一起的方法都应该有所帮助。这意味着同步它们或使用公共主时钟来合成其他频率。对于频率合成,我们需要一个 PLL(锁相环)或更好的 DLL(数字锁定环)。

近在 IEEE ISSCC 会议上发表的一篇论文[1] 讨论了一种用于乘法 DLL (MDLL) 的新型 IC 设计。MDLL 是频率合成器的。该设备可在 0.45V 的电源电压下工作,功耗为 423nW。显然,设计人员在设计这款 IC 时考虑到了手持设备。

使用 MDLL 时,您仍然需要其他(大多数)与主时钟(晶体振荡器)同步的自由运行振荡器。这些振荡器需要低功耗,并且应尽可能少地占用 PC 板空间。同样,该 IC 的设计人员找到了一种巧妙的方法来实现这一点。

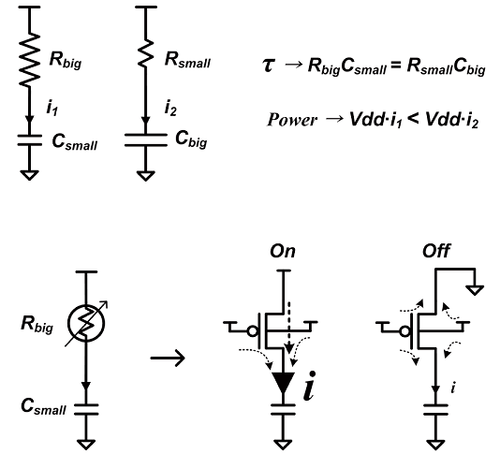

他们从概念上以 RC 网络开始,注意到对于任意低频,要么需要较大的 R 和较小的 C,要么反之亦然。使用较大的 R 版本,功耗会更小,因此设计师从那里开始。设计师没有尝试在硅中制造非常大值的电阻器,而是考虑到可控性的需求,采取了不同的方法。他们用 P 沟道 FET 代替电阻器作为电流源。他们利用 FET 的漏电特性,漏极接地或处于 (+) 电源电位(可切换)。

当 P-FET 的漏极连接到 +V 时,i LKG 为高电平;当漏极接地时,i LKG 为低电平。

这是数控振荡器的。他们使用多个 FET 电容网络来创建 MDLL。参考频率取自 32kHz 晶体振荡器。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 拥有点云数据的能否取代激光雷达?2025/8/11 16:25:52

- CAN XL 通信技术在车载毫米波雷达中的应用 (2)2025/8/8 16:24:00

- 光纤线和网线有啥区别2025/8/7 17:21:57

- 网线怎么排2025/8/1 11:42:44

- 全面对比:光纤线与网线的差异大揭秘2025/7/30 17:00:38