CD54/74HC540, CD74HCT540,

CD54/74HC541, CD54/74HCT541

Data sheet acquired from Harris Semiconductor

SCHS189C

January 1998 - Revised July 2004

High-Speed CMOS Logic

Octal Buffer and Line Drivers, Three-State

Description

The 鈥橦C540 and CD74HCT540 are Inverting Octal Buffers

and Line Drivers with Three-State Outputs and the capability

to drive 15 LSTTL loads. The 鈥橦C541 and 鈥橦CT541 are Non-

Inverting Octal Buffers and Line Drivers with Three-State Out-

puts that can drive 15 LSTTL loads. The Output Enables

(OE1) and (OE2) control the Three-State Outputs. If either

OE1 or OE2 is HIGH the outputs will be in the high imped-

ance state. For data output OE1 and OE2 both must be LOW.

Features

鈥?鈥橦C540, CD74HCT540 . . . . . . . . . . . . . . . . . . . Inverting

[ /Title

(CD74

HC540

,

CD74

HCT54

0,

CD74

HC541

,

CD74

HCT54

鈥?鈥橦C541, 鈥橦CT541 . . . . . . . . . . . . . . . . . . . . . . Non-Inverting

鈥?Buffered Inputs

鈥?Three-State Outputs

鈥?Bus Line Driving Capability

鈥?Typical Propagation Delay = 9ns at V

CC

= 5V,

C

L

= 15pF, T

A

= 25

o

C

鈥?Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

鈥?Wide Operating Temperature Range . . . -55

o

C to 125

o

C

鈥?Balanced Propagation Delay and Transition Times

鈥?Signi铿乧ant Power Reduction Compared to LSTTL

Logic ICs

鈥?HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30% of V

CC

at V

CC

= 5V

鈥?HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

鈮?/div>

1碌A at V

OL

, V

OH

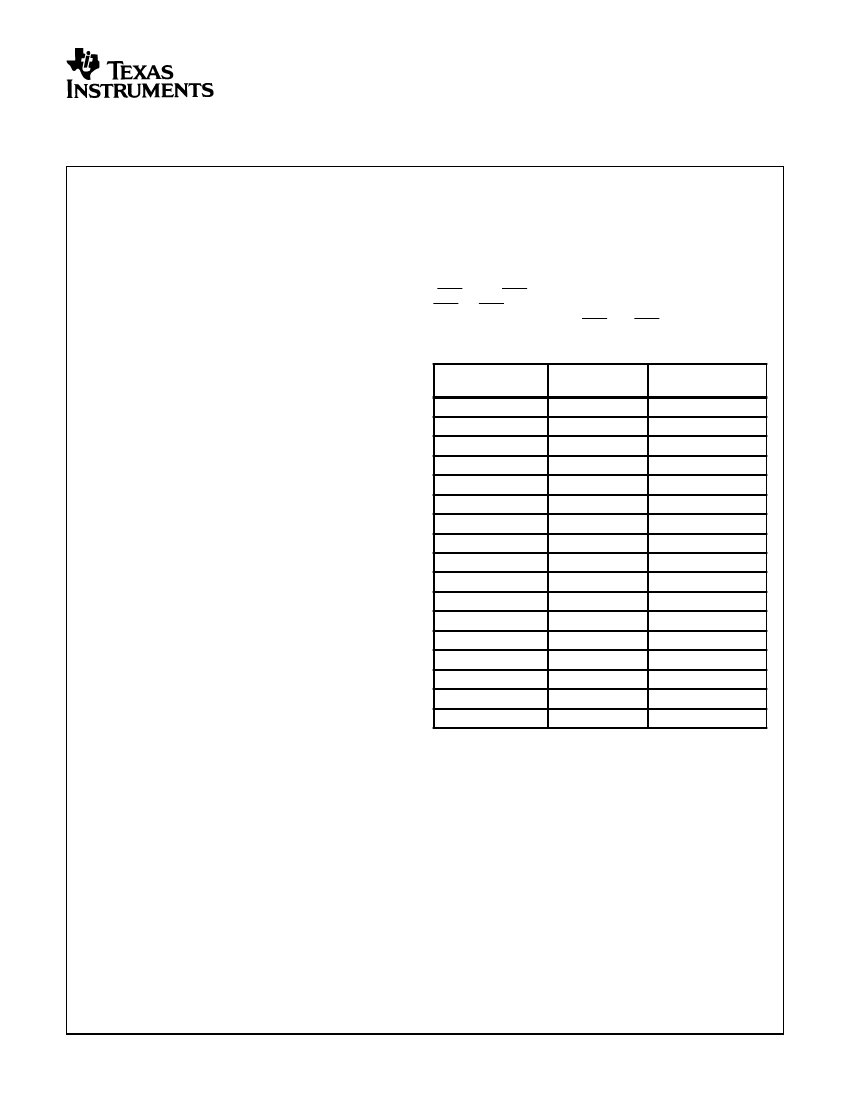

Ordering Information

PART NUMBER

CD54HC540F3A

CD54HC541F3A

CD54HCT541F3A

CD74HC540E

CD74HC540M

CD74HC540M96

CD74HC541E

CD74HC541M

CD74HC541M96

CD74HC541PW

CD74HC541PWR

CD74HCT540E

CD74HCT540M

CD74HCT540M96

CD74HCT541E

CD74HCT541M

CD74HCT541M96

TEMP. RANGE

(

o

C)

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

PACKAGE

20 Ld CERDIP

20 Ld CERDIP

20 Ld CERDIP

20 Ld PDIP

20 Ld SOIC

20 Ld SOIC

20 Ld PDIP

20 Ld SOIC

20 Ld SOIC

20 Ld TSSOP

20 Ld TSSOP

20 Ld PDIP

20 Ld SOIC

20 Ld SOIC

20 Ld PDIP

20 Ld SOIC

20 Ld SOIC

NOTE: When ordering, use the entire part number. The suf铿亁 96

denotes tape and reel.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

漏

2004, Texas Instruments Incorporated

1