鈩?/div>

Product Brief

Features

鈥?IEEE 802.3 Compatible Ethernet Controller

鈥?Integrated MAC and 10BASE-T PHY

鈥?8-Kbyte Transmit/Receive Packet Dual Port

Buffer SRAM

鈥?Receiver and Collision Squelch Circuit

鈥?Supports one 10BASE-T Port with Automatic

Polarity Detection and Correction

鈥?Programmable Automatic Retransmit on Collision

鈥?Programmable Padding and CRC Generation

鈥?Programmable Automatic Rejection of Erroneous

Packets

鈥?10 Mbit/s SPI鈩?Interface

鈥?Buffer:

- Configurable transmit/receive buffer size

- Hardware managed circular receive FIFO

- Byte-wide random and sequential access

- Internal DMA for fast memory copying

- Hardware assisted IP checksum calculation

鈥?MAC:

- Support for Unicast, Multicast and Broadcast

packets

- Programmable pattern matching

- Programmable wake-up on multiple packet

formats, including Magic Packet

庐

, Unicast,

Multicast, Broadcast, specific packet match

or any packet

- Loopback mode

鈥?PHY:

- Wave shaping output filter

- Loopback mode

鈥?Operational:

- Outputs for 2 LED indicators

- Transmit and receive interrupts

- 25 MHz clock

- Clock out pin with programmable prescaler

- Operating voltage range of 3.14V to 3.45V

- Temperature range: -40掳C to +85掳C Industrial,

0掳C to +70掳C Commercial (SSOP only)

鈥?28-pin SSOP, SOIC, SPDIP and QFN packages

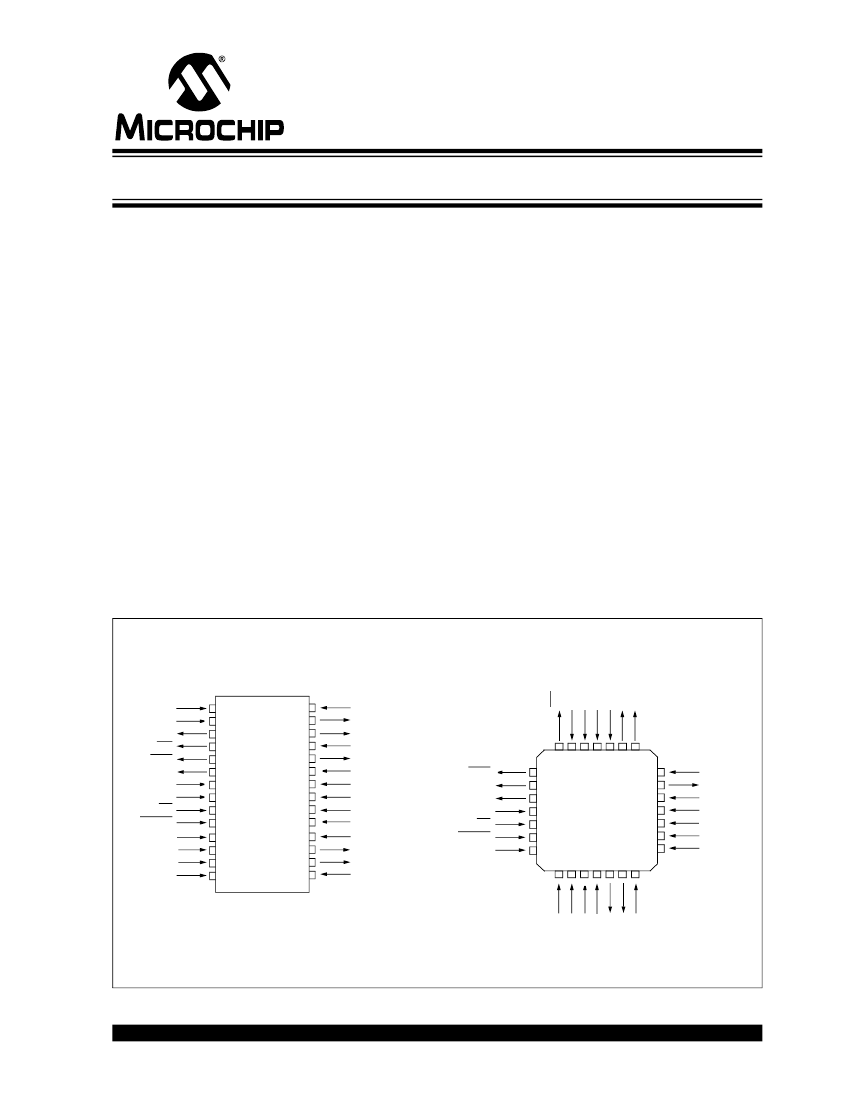

Pin Diagrams

28-pin SSOP, SOIC and SPDIP

28-pin QFN

CLKO

V

SS

V

CAP

V

DD

LEDA

LEDB

V

CAP

V

SS

CLKO

INT

WOL

SO

SI

SCK

CS

RESET

V

SSRX

TPIN-

TPIN+

RBIAS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

DD

LEDA

LEDB

V

DDOSC

OSC2

OSC1

V

SSOSC

V

SSPLL

V

DDPLL

V

DDRX

V

SSTX

TPOUT+

TPOUT-

V

DDTX

ENC28J60

INT

28 27 26 25 24 23 22

WOL

SO

SI

SCK

CS

RESET

V

SSRX

1

2

3

4

5

6

7

21

20

19

18

17

16

15

V

DDOSC

OSC2

OSC1

V

SSOSC

V

SSPLL

V

DDPLL

V

DDRX

ENC28J60

8 9 10 11 12 13 14

TPIN-

TPIN+

RBIAS

V

DDTX

铮?/div>

2004 Microchip Technology Inc.

Advance Information

TPOUT-

TPOUT+

V

SSTX

DS39623E-page 1