鈾?/div>

1,6%%!��

General Description

The IDT77301 UtopiaFIFO is a high-speed, low power single input

port supplying four demultiplexing FIFO output ports. Each of the four

output synchronous (clocked) FIFOs are 64 words (128 bytes) in depth.

Data is written to the input port in 鈥渃ells鈥?(fixed length data packets). The

cell size is programmable from 16 bytes to 128 bytes.

The input port can be configured to support 9-bit or 18-bit wide data

buses. (Multiple 77301鈥檚 can be configured to handle 32 and 64-bit buses

with no additional logic.)

There are four routing methods that can be used to transfer data to the

77301. Two methods use out-band routing for the port selection, which

requires use of the Address Location bus. The remaining two methods

support in-band routing, which uses the Address Location bus in conjunc-

tion with the Data bus for port selection. Utopia 2 signaling supports single

cell transfers to single output ports, but the 77301 also offers a proprietary

multicasting protocol. Multicasting enables a single cell to be transferred

simultaneously to multiple selected output ports.

The four output ports can be configured as 9-bit or 4-bit wide data

buses. (18-bit wide buses can be supported with multiple 77301鈥檚 with no

Data transfers on fixed cell sizes

Programmable cell size

One input port to four output ports

Four Independent output 128 x 9 FIFO Queues

Selectable eighteen bit or nine bit input bus

Selectable eight/nine bit or four bit output buses

Programmable chip Identification

鈥淯topiaTx鈥?level 2 compliant input interface signaling

鈥淯topiaTx鈥?level 1 compliant output interface signaling

Separate clocks for input and output

Selectable In-band or Out-band routing

Multicast capability

Data clock rates to 62.5 MHz, 10ns access time

Building Block Implementation allows up to 32 output channels with

a 18, 36 or 64-bit input bus

Four 562 Mbps output channels can be derived from a single

1.1256 Gbps input channel with no additional glue logic

100-pin TQPF package

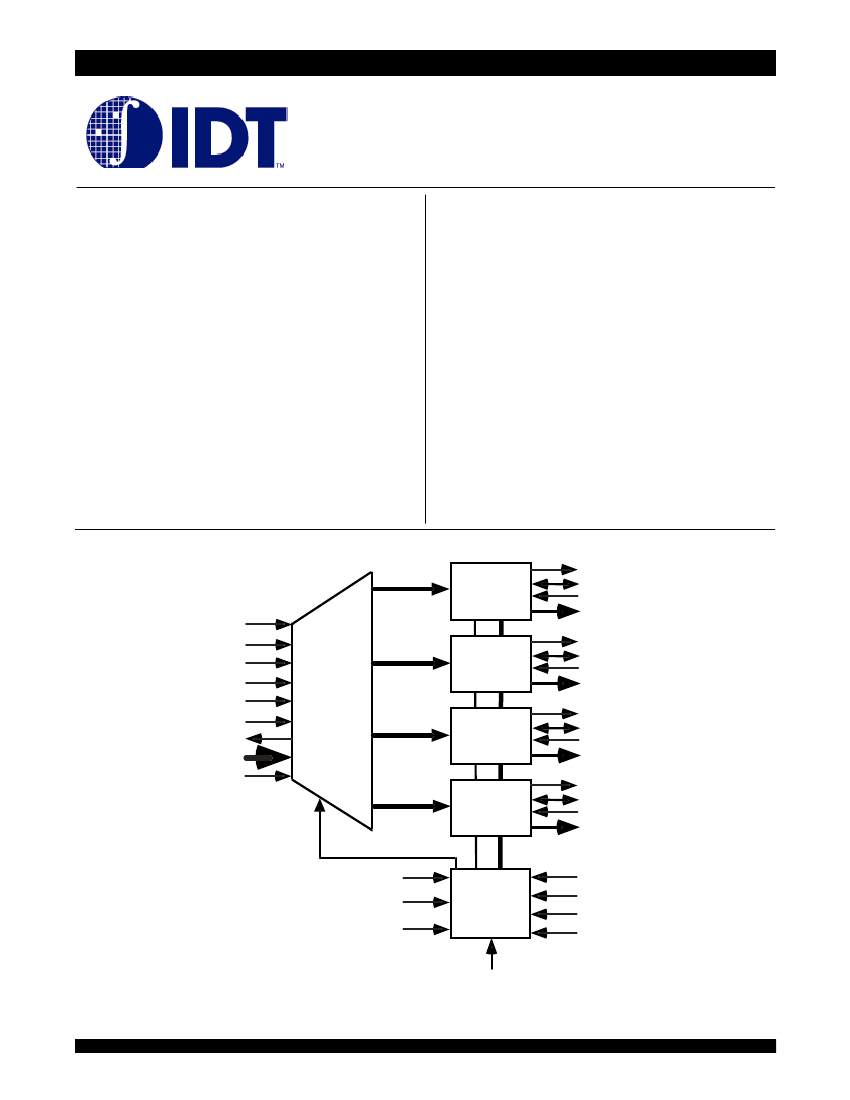

.unctional Block Diagram

128 BYTE

FIFO

RMS

MAS

BSS

ADR (0-4)

SOCR

SOCS - a

ENS

- a

CLAVS - a

Data - a (D0-D8)

SOCS - b

ENS

- b

CLAVS - b

Data - b (D0-D8)

SOCS - c

ENS

- c

CLAVS - c

Data - c (D0-D8)

SOCS - d

ENS

- d

CLAVS - d

Data - d (D0-D8)

128 BYTE

FIFO

ENR

CLAVR

Data (D0-D17)

WCLK

128 BYTE

FIFO

128 BYTE

FIFO

RST

MSE

BNE

CONTROL

REGISTER

RCLK

SLE

SCLK

SDI/P_ID0

3240 drw 01

OE

MARCH 2001

1

漏2001 Integrated Device Technology, Inc.

DSC-3240/3