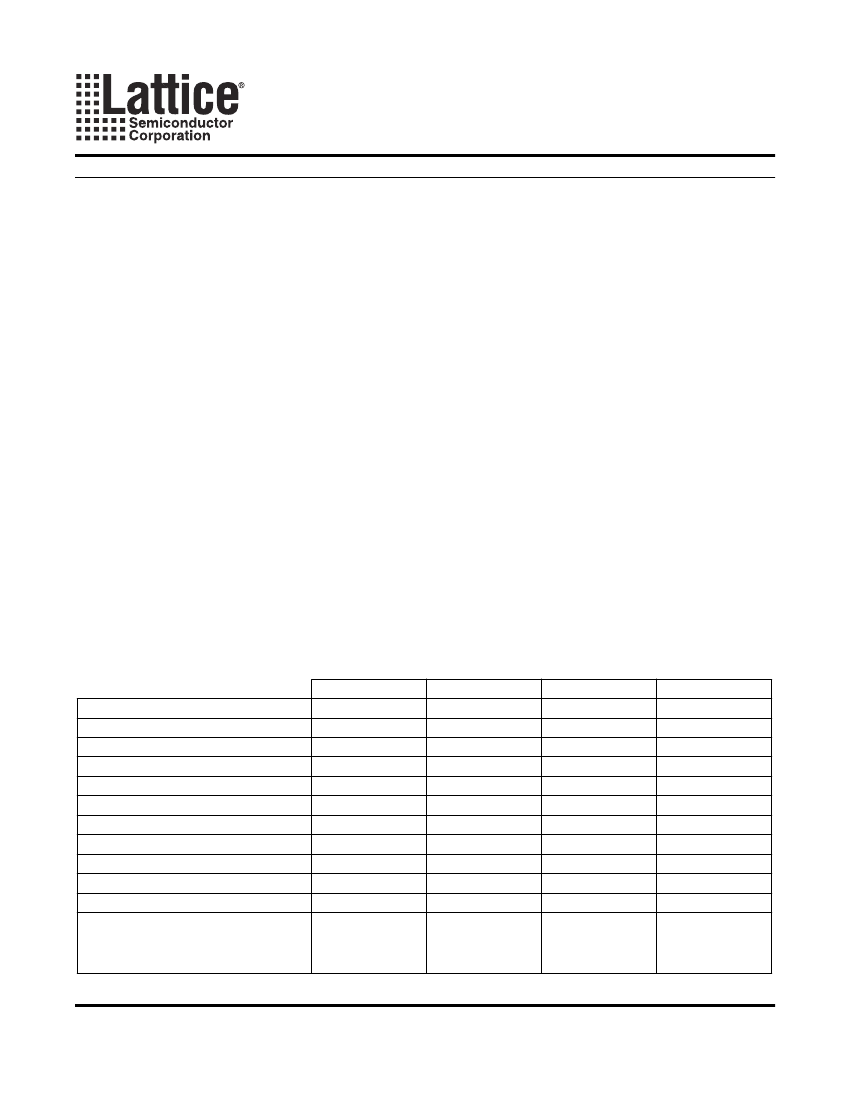

Table 1. ispXPLD 5000MX Family Selection Guide

鈻?/div>

Easy System Integration

鈥?3.3V (5000MV), 2.5V (5000MB) and 1.8V

(5000MC) power supply operation

鈥?5V tolerant I/O for LVCMOS 3.3 and LVTTL

interfaces

鈥?IEEE 1149.1 interface for boundary scan testing

鈥?sysIO quick con铿乬uration

鈥?Density migration

鈥?Multiple density and package options

鈥?PQFP and 铿乶e pitch BGA packaging

鈥?Lead-free package options

ispXPLD 5512MX

512

16

256K

96K

2

4.5ns

2.8ns

3.0ns

275MHz

150K

149/193/253

208 PQFP

256 fpBGA

484 fpBGA

ispXPLD 5768MX ispXPLD 51024MX

768

24

384K

144K

2

5.0ns

2.8ns

3.2ns

250MHz

225K

193/317

256 fpBGA

484 fpBGA

1,024

32

512K

192K

2

5.2ns

3.0ns

3.7ns

250MHz

300K

317/381

484 fpBGA

672 fpBGA

漏 2004 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The speci铿乧ations and information herein are subject to change without notice.

www.latticesemi.com

1

5kmx_10