PIC18F6390/6490/8390/8490

PIC18F6390/6490/8390/8490 Rev. B3 Silicon Errata

The PIC18F6390/6490/8390/8490 Rev. B3 parts you

have received conform functionally to the Device Data

Sheet (DS39629), except for the anomalies described

below. Any Data Sheet Clarification issues related to

the PIC18F6390/6490/8390/8490 will be reported in a

separate Data Sheet errata. Please check the

Microchip web site for any existing issues.

All of the issues listed here will be addressed in future

revisions of the PIC18F6390/6490/8390/8490 silicon.

The following silicon errata apply only to

PIC18F6390/6490/8390/8490 devices with these

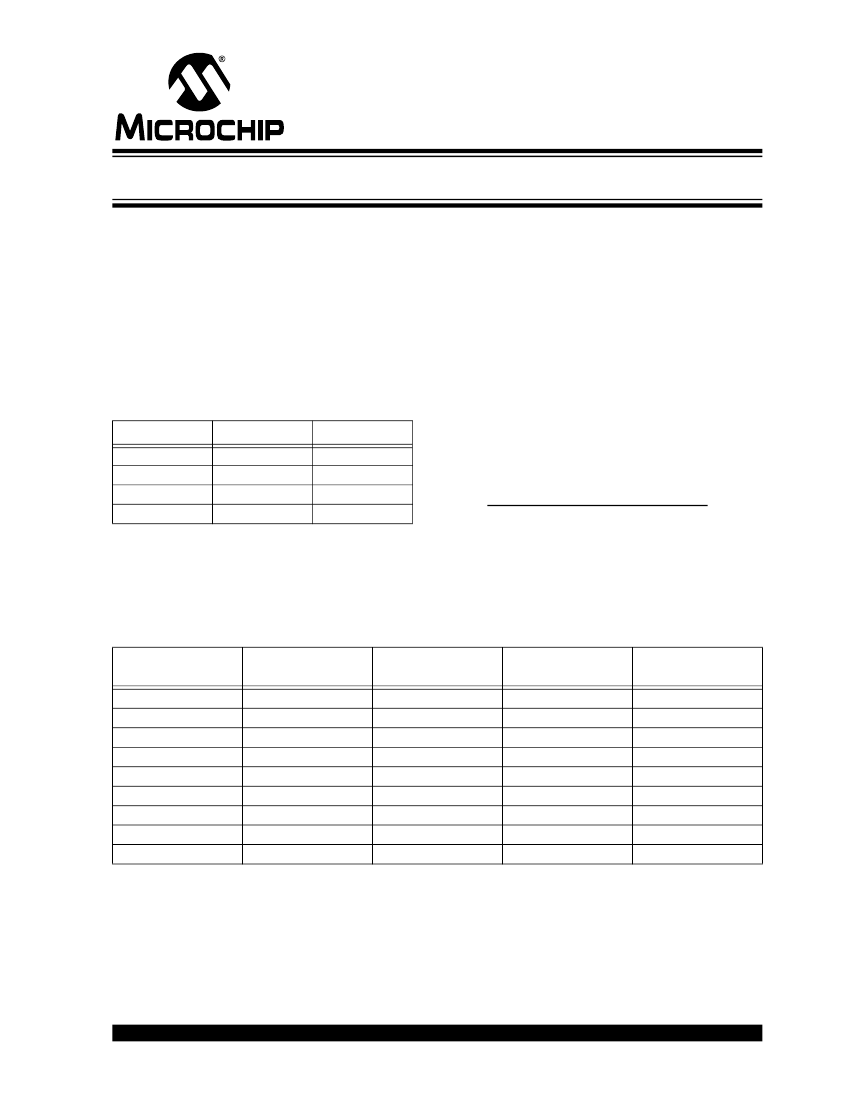

Device/Revision IDs:

Part Number

PIC18F6390

PIC18F6490

PIC18F8390

PIC18F8490

Device ID

00 1011 101

00 0110 101

00 1101 100

00 0110 100

Revision ID

00011

00011

00011

00011

1. Module: MSSP

In its current implementation, the I

2

C鈩?Master

mode operates as follows:

a) The Baud Rate Generator for I

2

C in Master

mode is slower than the rates specified in

Table 15-3 of the Device Data Sheet.

For this revision of silicon, use the values

shown in Table 1 in place of those shown in

Table 15-3 of the Device Data Sheet. The

differences are shown in

bold

text.

b) Use the following formula in place of the one

shown in Register 15-4 (SSPCON1) of the

Device Data Sheet for bit description

SSPM3:SSPM0 =

1000.

SSPADD = INT((F

CY

/F

SCL

) 鈥?(F

CY

/1.111 MHz)) 鈥?1

Date Codes that pertain to this issue:

All engineering and production devices.

The Device IDs (DEVID1 and DEVID2) are located at

addresses 3FFFFEh:3FFFFFh in the device鈥檚

configuration space. They are shown in hexadecimal

in the format 鈥淒EVID2 DEVID1鈥?

TABLE 1:

F

OSC

40 MHz

40 MHz

40 MHz

16 MHz

16 MHz

16 MHz

4 MHz

4 MHz

4 MHz

Note 1:

I

2

C鈩?CLOCK RATE w/BRG

F

CY

10 MHz

10 MHz

10 MHz

4 MHz

4 MHz

4 MHz

1 MHz

1 MHz

1 MHz

F

CY

* 2

20 MHz

20 MHz

20 MHz

8 MHz

8 MHz

8 MHz

2 MHz

2 MHz

2 MHz

BRG Value

0Eh

15h

59h

05h

08h

23h

01h

08h

00h

F

SCL

(2 Rollovers of BRG)

400 kHz

(1)

312.5 kHz

100 kHz

400 kHz

(1)

308 kHz

100 kHz

333 kHz

(1)

100 kHz

1 MHz

(1)

The I

2

C鈩?interface does not conform to the 400 kHz I

2

C specification (which applies to rates greater than

100 kHz) in all details, but may be used with care where higher rates are required by the application.

漏

2005 Microchip Technology Inc.

DS80207B-page 1