过零比较和相位比较电路原理图

出处:jjpsl 发布于:2009-11-26 00:00:00 | 4284 次阅读

现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图1所示。

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

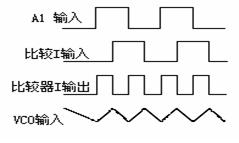

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。上述波形如图2.13所示。由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

图2 比较器输出波形图

上一篇:高速电压跟随器电路图

下一篇:直流调压电路图

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。