Lattice Semiconductor

True Dual-Port SRAM Mode

ispXPLD 5000MX Family Data Sheet

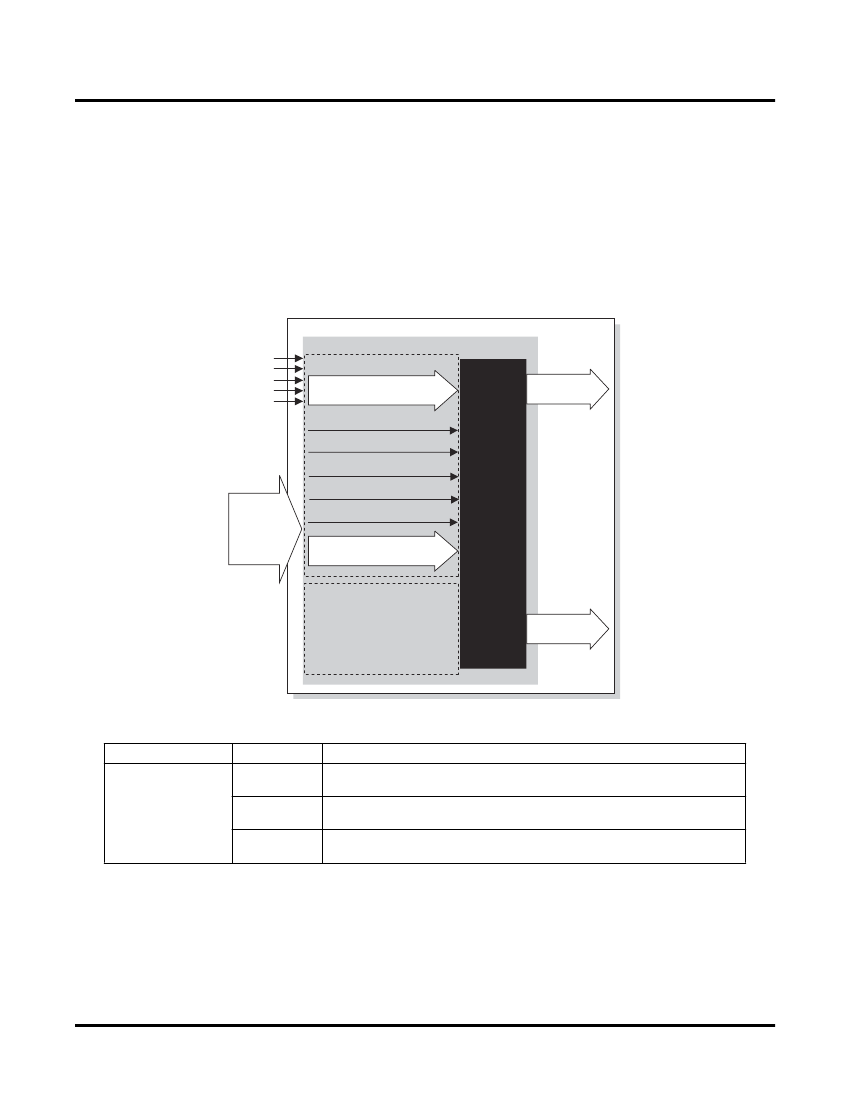

In Dual-Port SRAM Mode the multi-function array is con铿乬ured as a dual port SRAM. In this mode two independent

read/write ports access the same 8,192-bits of memory. Data widths of 1, 2, 4, 8, and 16 are supported by the

MFB. Figure 9 shows the block diagram of the dual port SRAM.

Write data, address, chip select and read/write signals are always synchronous (registered.) The output data sig-

nals can be synchronous or asynchronous. Resets are asynchronous. All inputs on the same port share the same

clock, clock enable, and reset selections. All outputs on the same port share the same clock, clock enable, and

reset selections. Selections may be made independently between both inputs and outputs and ports. Table 5

shows the possible sources for the clock, clock enable and initialization signals for the various registers.

Figure 9. Dual-Port SRAM Block Diagram

CLK0

CLK1

CLK2

CLK3

RESET

PORT

A

Read/Write Address

(ADA[0:8-12])

RD Data A

(DOA[0:0-15])

Reset A

(RSTA)

Clock A

(CLKA)

Clk En A

(CENA)

Write/Read A

(WRA)

68 Inputs

From

Routing

Chip Sel A

(CSA [0:1])

Write Data

(DIA[0:0,1,3,7,15])

鈥?/div>

鈥?/div>

Dual

Port

SRAM

Array

PORT B

Similar signals

as PORT A:

ADB[0:8-12], RSTB,

CLKB, CENB, WRB,

CSB[0,1], DIB[0:0,1,3,7,15]

RD Data B

(DOB[0:0-15])

Table 5. Register Clock, Clock Enable, and Reset in Dual-Port SRAM Mode

Register

Address, Write Data,

Read Data, Read/

Write, and Chip

Select

Input

Clock

Clock Enable

Reset

Source

CLKA (CLKB) or one of the global clocks (CLK0 - CLK3). The selected sig-

nal can be inverted if desired.

CENA (CENB) or one of the global clocks (CLK1 - CLK 2). The selected sig-

nal can be inverted if required.

Created by the logical OR of the global reset signal and RSTA (RSTB).

RSTA (RSTB) can be inverted is desired.

10