Lattice Semiconductor

FIFO Mode

ispXPLD 5000MX Family Data Sheet

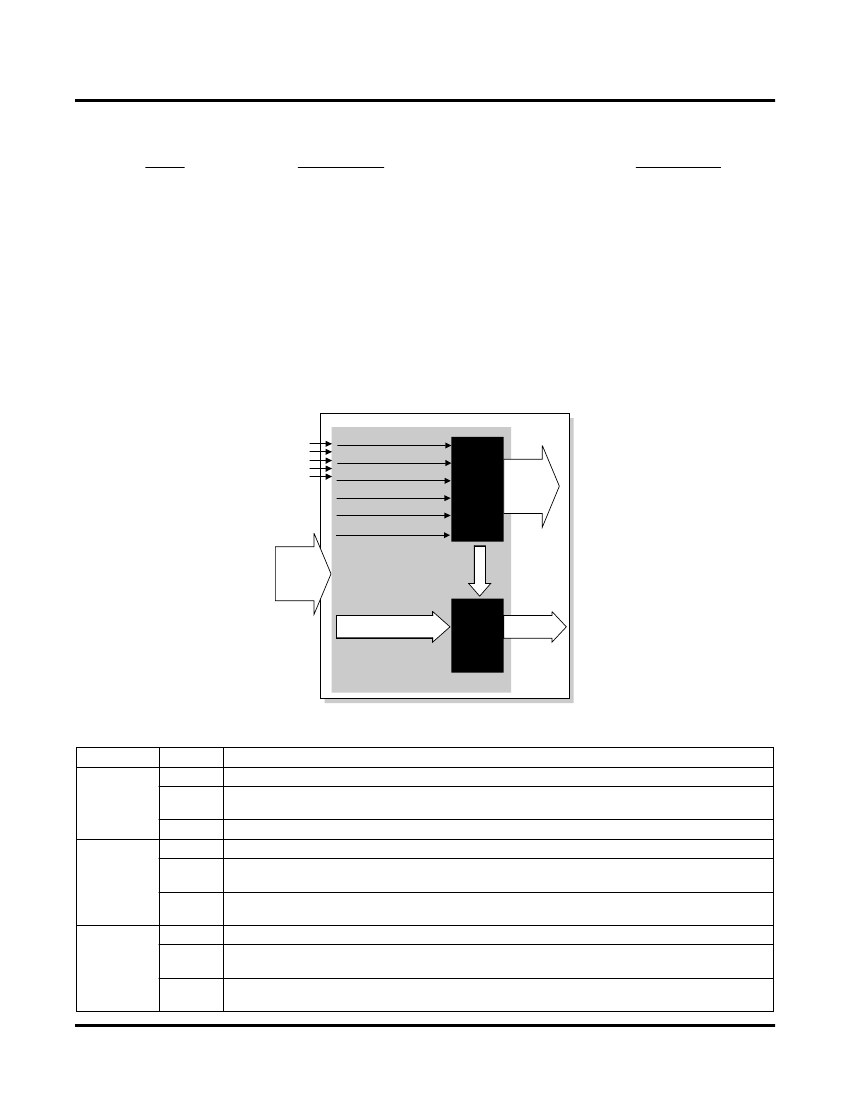

In FIFO Mode the multi-function array is con铿乬ured as a FIFO (First In First Out) buffer with built in control. The

read and write clocks can be different or the same dependent on the application. Four 铿俛gs show the status of the

FIFO; Full, Empty, Almost Full, and Almost Empty. The thresholds for Full, Almost full and Almost empty are pro-

grammable by the user. It is possible to reset the read pointer, allowing support of frame retransmit in communica-

tions applications. If desired, the block can be used in show ahead mode allowing the early reading of the next read

address.

In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the

MFB. Figure 12 shows the block diagram of the FIFO.

Write data, write enable, 铿俛g outputs and read enable are synchronous. The Write Data, Almost Full and Full share

the same clock and clock enables. Read outputs are synchronous although these can be con铿乬ured in look ahead

mode. The Read Data, Empty and Almost Empty signals share the same clock and clock enables. Reset is shared

by all signals. Table 8 shows the possible sources for the clock, clock enable and reset signals for the various reg-

isters.

Figure 12. FIFO Block Diagram

Write Enable

(WE)

Write Clock

(WCLK)

Reset

(RST)

CLK0

CLK1

CLK2

CLK3

RESET

Read Clock

(RCLK)

Reset_RP

(RSTRP)

FIFO

Control

Logic

FIFO

Flags*

Full,

Empty,

Almost Full,

Almost Empty

Read Enable

(RE)

鈥?/div>

鈥?/div>

68 Inputs

From

Routing

Write Data

(DI[0:0-31])

16,384-bit

Read Data

(DO[0:0-31])

SRAM

Array

*Control logic can be

duplicated in adjacent MFB

in 32-bit mode

Table 8. Register Clocks, Clock Enables, and Initialization in FIFO Mode

Register

Input

Source

WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.

WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.

N/A

WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.

WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.

Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction

array from GRP, with inversion if desired.

RCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.

RE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.

Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction

array from GRP, with inversion if desired.

Write Data,

Clock

Write Enable Clock

Enable

Reset

Full and

Almost Full

Flags

Clock

Clock

Enable

Reset

Read Data,

Clock

Empty and

Clock

Almost Empty Enable

Flags

Reset

13