Lattice Semiconductor

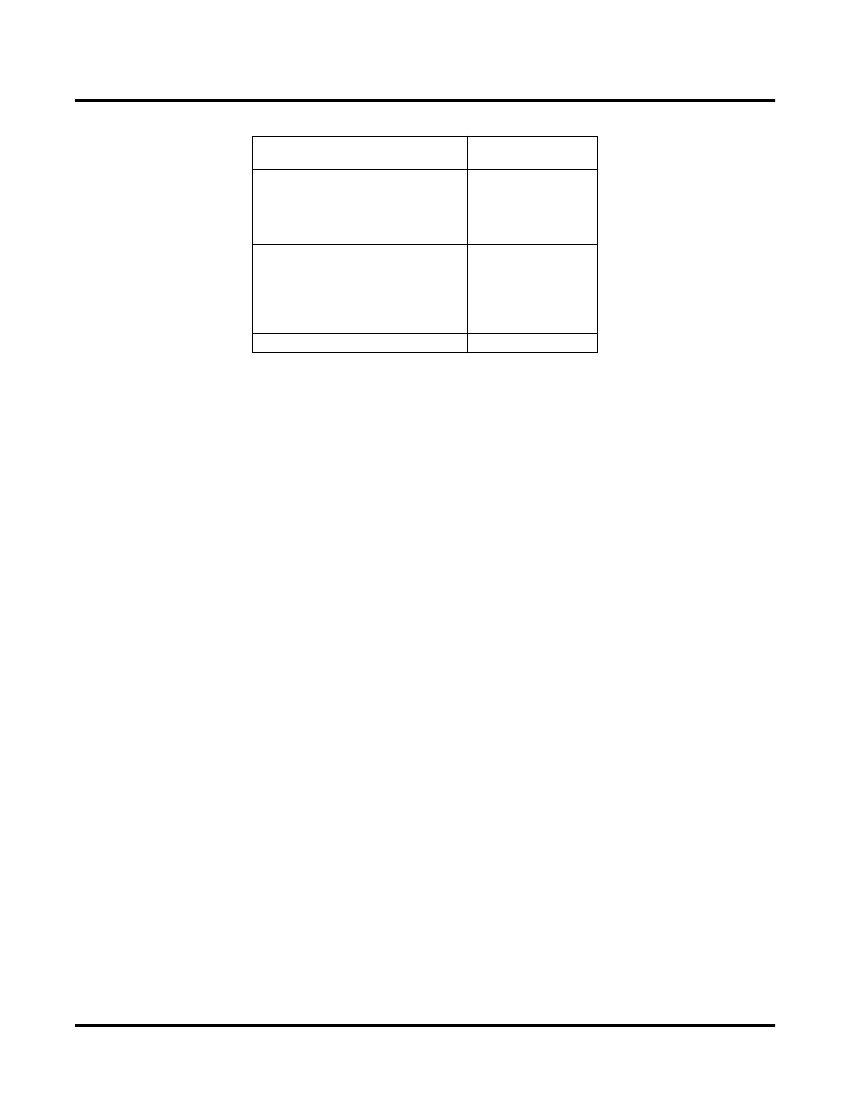

Table 4. MFB Memory Con铿乬uration

Memory Mode

Dual-port

ispXPLD 5000MX Family Data Sheet

Max. Con铿乬uration

Size

1

8,192 x 1

4,096 x 2

2,048 x 4

1,024 x 8

512 x 16

16,384 x1

8,192 x 2

4,096 x 4

2,048 x 8

1,024 x 16

512 x 32

128 x 48

Single-port, Pseudo Dual Port, FIFO

CAM

1. Smaller con铿乬urations are possible.

Input and Output

The data input and control signals to a MFB in memory mode are generated from inputs from the routing. Data sig-

nals are only available in the true non-inverted format. True or complemented versions of the inputs are available

for generating the control signals. Data and 铿俛g outputs are fed from the MFB to the GRP and OSA. Unused inputs

and outputs are not accessible in memory mode.

ROM Operation

In each of the memory modes it is possible to specify the power-on state of each bit in the memory array. This

allows the memory to be used as ROM if desired.

Increased Depth And Width

Designs that require a memory depth or width that is greater than that support by a single MFB can be supported

by cascading multiple blocks. For dual port, single port, and pseudo dual port modes additional width is easily pro-

vided by sharing address lines. Additional depth is supported by multiplexing the RAM output. For FIFO and CAM

modes additional width is supported through the cascading of MFBs.

The Lattice design tools automatically combine blocks to support the memory size speci铿乪d in the user鈥檚 design.

Bus Size Matching

All of the memory modes apart from CAM mode support different widths on each of the ports. The RAM bits are

mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of

words for each port varies this mapping scheme applies to each port.

9