Cyclone FPGA Family Data Sheet

Preliminary Information

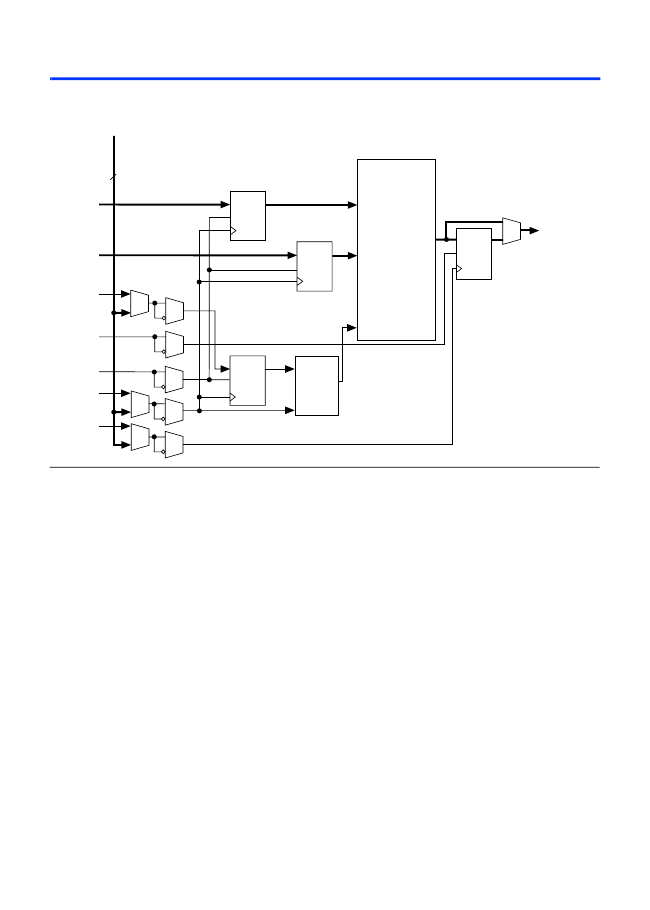

Figure 21. Single-Port Mode

6 LAB Row

Clocks

6

data[ ]

D

Q

ENA

RAM/ROM

256

脳

16

512

脳

8

1,024

脳

4

Data In

2,048

脳

2

4,096

脳

1

Data Out

D

Q

ENA

To MultiTrack

Interconnect

address[ ]

D

Q

ENA

Address

wren

Write Enable

outclken

inclken

inclock

D

Q

ENA

Write

Pulse

Generator

outclock

Global Clock

Network &

Phase-Locked

Loops

Cyclone devices provide a global clock network and up to two PLLs for a

complete clock management solution.

Global Clock Network

There are four dedicated clock pins (CLK[3..0], two pins on the left side

and two pins on the right side) that drive the global clock network, as

shown in

Figure 22.

PLL outputs, logic array, and dual-purpose clock

(DPCLK[7..0]) pins can also drive the global clock network.

The eight global clock lines in the global clock network drive throughout

the entire device. The global clock network can provide clocks for all

resources within the device铮OEs, LEs, and memory blocks. The global

clock lines can also be used for control signals, such as clock enables and

synchronous or asynchronous clears fed from the external pin, or DQS

signals for DDR SDRAM or FCRAM interfaces. Internal logic can also

drive the global clock network for internally generated global clocks and

asynchronous clears, clock enables, or other control signals with large

fanout.

Figure 22

shows the various sources that drive the global clock

network.

34

Altera Corporation