256-Mbit J3 (x8/x16)

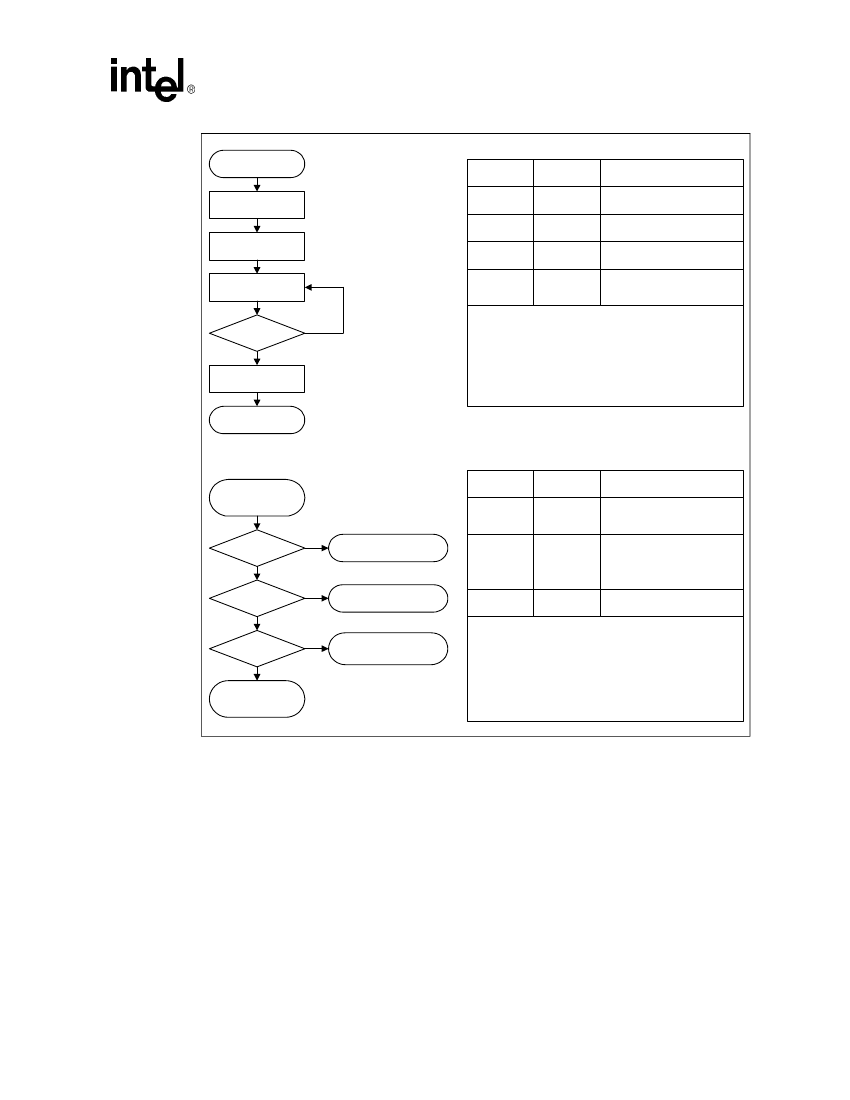

Figure 20. Byte/Word Program Flowchart

Start

Bus

Operation

Write

Write

Command

Setup Byte/

Word Program

Byte/Word

Program

Comments

Data = 40H

Addr = Location to Be Programmed

Data = Data to Be Programmed

Addr = Location to Be Programmed

Status Register Data

Check SR.7

1 = WSM Ready

0 = WSM Busy

Write 40H,

Address

Write Data and

Address

Read Status

Register

0

1

Full Status

Check if Desired

Byte/Word

Program Complete

Read

(Note 1)

Standby

SR.7 =

1. Toggling OE# (low to high to low) updates the status register. This

can be done in place of issuing the Read Status Register command.

Repeat for subsequent programming operations.

SR full status check can be done after each program operation, or

after a sequence of programming operations.

Write FFH after the last program operation to place device in read

array mode.

FULL STATUS CHECK PROCEDURE

Read Status

Register Data

(See Above)

1

SR.3 =

0

SR.1 =

0

1

SR.4 =

0

Byte/Word

Program

Successful

Programming Error

Voltage Range Error

Standby

Bus

Operation

Standby

Command

Comments

Check SR.3

1 = Programming to Voltage Error

Detect

Check SR.1

1 = Device Protect Detect

RP# = V

IH

, Block Lock-Bit Is Set

Only required for systems

implemeting lock-bit configuration.

Check SR.4

1 = Programming Error

1

Device Protect Error

Standby

Toggling OE# (low to high to low) updates the status register. This can

be done in place of issuing the Read Status Register command.

Repeat for subsequent programming operations.

SR.4, SR.3 and SR.1 are only cleared by the Clear Status Register

command in cases where multiple locations are programmed before

full status is checked.

If an error is detected, clear the status register before attempting retry

or other error recovery.

Datasheet

61