256-Mbit J3 (x8/x16)

suspended (and programming is inactive), program is suspended, or the device is in reset/power-

down mode. Additionally, the configuration command allows the STS signal to be configured to

pulse on completion of programming and/or block erases.

Three CE signals are used to enable and disable the device. A unique CE logic design (see

Table 13, 鈥淐hip Enable Truth Table鈥?on page 33)

reduces decoder logic typically required for

multi-chip designs. External logic is not required when designing a single chip, a dual chip, or a 4-

chip miniature card or SIMM module.

The BYTE# signal allows either x8 or x16 read/writes to the device. BYTE#-low selects 8-bit

mode; address A0 selects between the low byte and high byte. BYTE#-high enables 16-bit

operation; address A1 becomes the lowest order address and address A0 is not used (don鈥檛 care). A

device block diagram is shown in Figure 4 on page 14.

When the device is disabled (see

Table 13 on page 33),

with CEx at V

IH

and RP# at V

IH

, the

standby mode is enabled. When RP# is at V

IL

, a further power-down mode is enabled which

minimizes power consumption and provides write protection during reset. A reset time (t

PHQV

) is

required from RP# going high until data outputs are valid. Likewise, the device has a wake time

(t

PHWL

) from RP#-high until writes to the CUI are recognized. With RP# at V

IL

, the WSM is reset

and the Status Register is cleared.

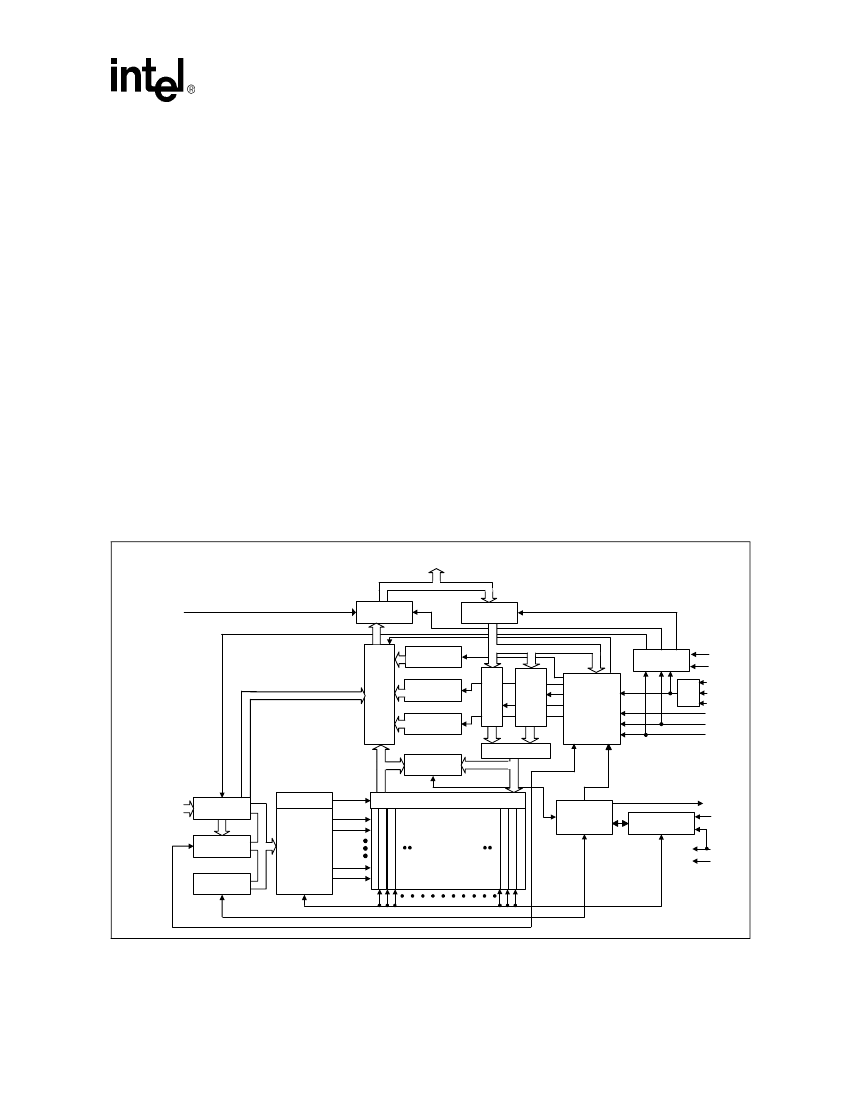

2.1

Block Diagram

Figure 1. 3 Volt Intel StrataFlash

庐

Memory Block Diagram

D[15:0]

VCCQ

Output

Buffer

Input Buffer

Query

Output

Latch/Multiplexer

Write Buffer

Identifier

Register

Status

Register

I/O Logic

Data

Register

CE

Logic

VCC

BYTE#

CE0

CE1

CE2

WE#

OE#

RP#

Command

User

Interface

A[2:0]

Multiplexer

Data

Comparator

Y-Decoder

A[MAX:MIN]

Input Buffer

Y-Gating

32-Mbit: Thirty-two

64-Mbit: Sixty-four

128-Mbit: One-hundred

twenty-eight

128-Kbyte Blocks

Write State

Machine

Program/Erase

Voltage Switch

STS

VPEN

Address

Latch

Address

Counter

X-Decoder

VCC

GND

Datasheet

9