TMS320VC5416

Fixed-Point Digital Signal Processor

SPRS095O 鈥?MARCH 1999 鈥?REVISED JANUARY 2005

www.ti.com

15

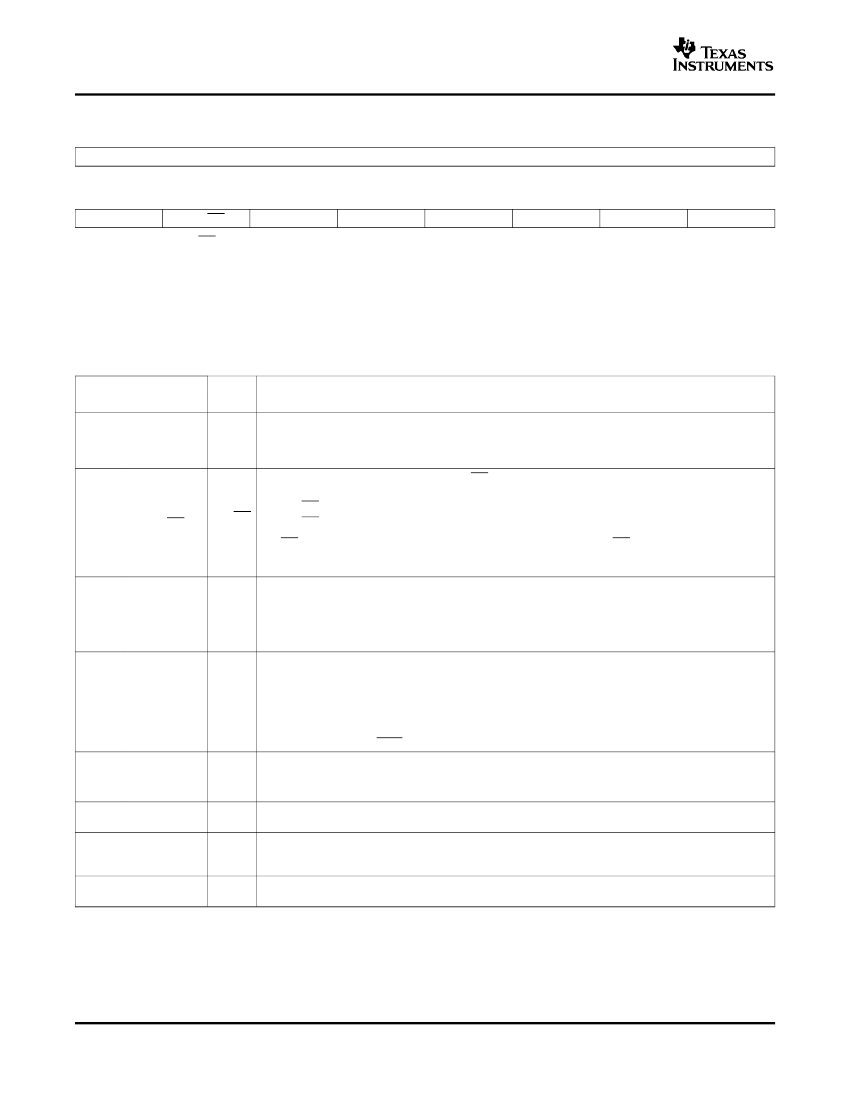

IPTR

R/W-1FF

7

IPTR

6

MP/MC

5

OVLY

4

AVIS

3

DROM

R/W-0

2

CLKOFF

R/W-0

1

SMUL

R/W-0

8

0

SST

R/W-0

MP/MC pin

R/W-0

R/W-0

LEGEND:

R = Read, W = Write,

n

= value present after reset

Figure 3-4. Process Mode Status Register

Table 3-2. Processor Mode Status (PMST) Register Bit Fields

BIT

NO.

15-7

NAME

IPTR

RESET

VALUE

FUNCTION

Interrupt vector pointer. The 9-bit IPTR field points to the 128-word program page where the interrupt

vectors reside. The interrupt vectors can be remapped to RAM for boot-loaded operations. At reset,

these bits are all set to 1; the reset vector always resides at address FF80h in program memory space.

The RESET instruction does not affect this field.

1FFh

6

MP/MC

Microprocessor/microcomputer mode. MP/MC enables/disables the on-chip ROM to be addressable in

program memory space.

鈥?/div>

MP/MC = 0: The on-chip ROM is enabled and addressable.

MP/MC

鈥?/div>

MP/MC = 1: The on-chip ROM is not available.

pin

MP/MC is set to the value corresponding to the logic level on the MP/MC pin when sampled at reset.

This pin is not sampled again until the next reset. The RESET instruction does not affect this bit. This

bit can also be set or cleared by software.

RAM overlay. OVLY enables on-chip dual-access data RAM blocks to be mapped into program space.

The values for the OVLY bit are:

鈥?/div>

OVLY = 0: The on-chip RAM is addressable in data space but not in program space.

鈥?/div>

OVLY = 1: The on-chip RAM is mapped into program space and data space. Data page 0

(addresses 0h to 7Fh), however, is not mapped into program space.

Address visibility mode. AVIS enables/disables the internal program address to be visible at the

address pins.

鈥?/div>

AVIS = 0: The external address lines do not change with the internal program address. Control

and data lines are not affected and the address bus is driven with the last address on the bus.

鈥?/div>

AVIS = 1: This mode allows the internal program address to appear at the pins of the device so

that the internal program address can be traced. Also, it allows the interrupt vector to be decoded

in conjunction with IACK when the interrupt vectors reside on on-chip memory.

DROM enables on-chip DARAM4-7 to be mapped into data space. The DROM bit values are:

鈥?/div>

DROM = 0: The on-chip DARAM4-7 is not mapped into data space.

鈥?/div>

DROM = 1: The on-chip DARAM4-7 is mapped into data space.

CLOCKOUT off. When the CLKOFF bit is 1, the output of CLKOUT is disabled and remains at a high

level.

Saturation on multiplication. When SMUL = 1, saturation of a multiplication result occurs before

performing the accumulation in a MAC of MAS instruction. The SMUL bit applies only when OVM = 1

and FRCT = 1.

Saturation on store. When SST = 1, saturation of the data from the accumulator is enabled before

storing in memory. The saturation is performed after the shift operation.

5

OVLY

0

4

AVIS

0

3

DROM

0

2

1

0

CLKOFF

SMUL

SST

0

N/A

N/A

22

Functional Overview

TMS320VC5416GGU160相关型号PDF文件下载

-

型号

版本

描述

厂商

下载

-

英文版

SECOND-GENERATION DIGITAL SIGNAL PROCESSORS

TI

-

英文版

SECOND-GENERATION DIGITAL SIGNAL PROCESSORS

TI [Texas ...

-

英文版

GRAPHICS SYSTEM PROCESSOR

TI

-

英文版

Graphics Library

-

英文版

C Source Debugger User Guide

-

英文版

RADIO FREQUENCY I DENTIFICATION SYSTEMS

TI

-

英文版

Family Simulator Getting Started Guide

-

英文版

Programming Tool Getting Started Guide

-

英文版

Microcontroller Family User抯 Guide

-

英文版

C Source Debugger User Guide

-

英文版

Microcontroller/Gang Programmer

-

英文版

DUAL 25-BIT STATIC SHIFT REGISTER

TI [Texas ...

-

英文版

DUAL 25-BIT STATIC SHIFT REGISTER

TI [Texas ...

-

英文版

QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS

TI

-

英文版

QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS

TI [Texas ...

-

英文版

QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS

TI

-

英文版

QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS

TI [Texas ...

-

英文版

HEX 32-BIT STATIC SHIFT REGISTERS

TI

-

英文版

HEX 32-BIT STATIC SHIFT REGISTERS

TI [Texas ...

-

英文版

HEX 32-BIT STATIC SHIFT REGISTERS

TI