not permitted while ISP flash EEPROM program memory is

being programmed.

The ISP flash memory is divided into 192 pages, each page

containing 4 words (each 16 bits wide). Each page is further

divided into two rows. Erase is carried out one page at a time,

whereas programming is carried out one row (or one partial

row) at a time.

Once an erase or programming operation is started, the PG-

MBUSY bit in the MSTAT register is automatically set, and

then cleared when the operation is complete. All high-voltage

pulses and timing needed for programming and erasing are

provided internally. The program memory cannot be access-

ed while the PGMBUSY bit is set.

Erase Procedure

Erasing a page requires the following code sequence:

1.

2.

3.

4.

5.

6.

7.

Verify that the MSTAT.PGMBUSY bit is cleared.

Set the DMCSR.ERASE bit to 1.

Locally disable interrupts.

Write proper key value to the ISPKEY register.

Write to any valid page to be erased.

Re-enable interrupts disabled in Step 3.

Set the DMCSR.ERASE bit to 0.

Programming Procedure

through a byte write instruction when the write instruction is

anywhere within the user boot ROM area (defined above) ex-

cept for the last two words. When the user boot ROM area

has been disabled, this word cannot be programmed in the

IRE environment. Note that when this word is erased for re-

programming, the other words in the same page must first be

saved, and then re-programmed.

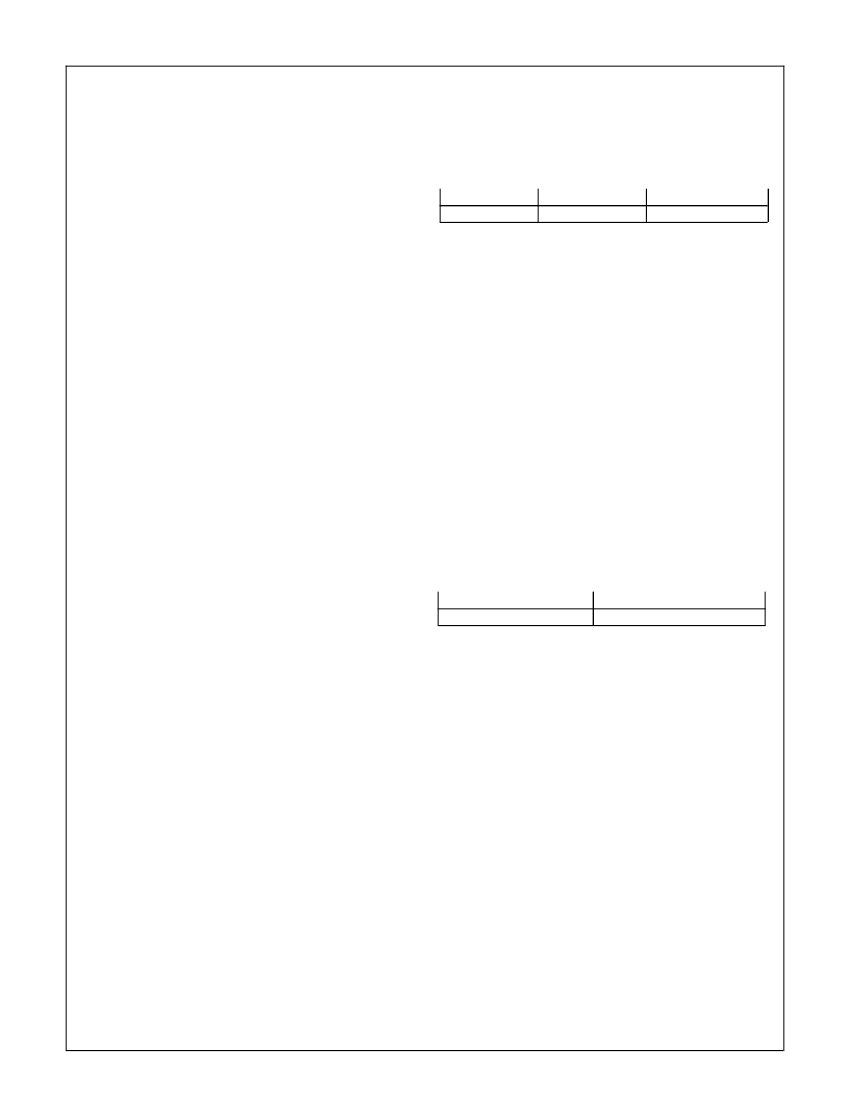

7

EMPTY

5

4

2

1

0

Reserved

CODEAREA[9:8]

9.4.3

Programming is done by writing one byte or word at a time

and should be done on already erased memory.

Programming the ISP flash EEPROM program memory re-

quires the following code sequence:

1.

2.

3.

4.

5.

Verify that the MSTAT.PGMBUSY bit is cleared.

Locally disable interrupts.

Write proper key value to the ISPKEY register.

Write a byte or word to the addressed location.

Re-enable interrupts disabled in Step 2.

CODEAREA[9:8]

The 2 least significant bits in address E5FE

contains the two most significant bits of the 10-

bit CODEAREA field. The description of

CODEAREA is shown in the E5FC section.

EMPTY

The EMPTY status indicates if the flash EE-

PROM program memory array is empty or not.

It is located in the 3 most significant bits in ad-

dress E5FE. When two or more bits in the

EMPTY field are set, the flash EEPROM pro-

gram memory is empty. Upon reset of the de-

vice and the environment select pins are all

high, the device operates in ISP environment

rather than IRE environment. After the program

memory has been filled with user code, this

field should be cleared to 000

2

.

000, 001, 010, 100: Program memory contains user code

011, 101, 11x: Program memory is empty, do not start up in IRE

E5FF Byte

Upon reset, the byte located in the E5FF address is read into

the FLSEC register. This byte cannot be written to in the IRE

environment. The format of the E5FF byte is shown below:

7

FROMWR

4

3

FROMRD

0

Programmed values can be verified through normal read op-

erations.

If a reset occurs in the middle of an erase or programming

operation, the operation is terminated. The reset is extended

until the flash EEPROM memory returns to the idle state.

9.4.4

Erase and Programming Timing

The FROMRD and FROMWR fields in address location

E5FF respectively provide read and write security to the flash

EEPROM program memory array while executing instruc-

tions in all environments except IRE. The user should always

write 0000

2

to enable security feature.

0000, 0001, 0010, 0100, 1000: Security feature enabled

0011, 0101, 011x, 1001, 101x, 11xx: Security feature disabled

The program and erase timing are controlled by the flash EE-

PROM data memory logic.

9.4.5

Memory Control and Protection Features

FROMRD

The last 8 bytes of the ISP memory are reserved for special

functions and some of these bytes provide memory protec-

tion and security for the flash EEPROM program memory.

Read and various types of write protection are provided.

During the reset stretch period, bytes located at E5FE and

E5FF are read out to the FLCTRL2 and FLSEC registers re-

spectively. Upon reset and before an instruction fetch, bytes

located at E5FC and E5FD are read out to the FLCTRL2 and

FLCTRL1 registers respectively. Parts of FLCTRL2 register

are loaded at different times.

E5FE Byte

Upon reset of the chip, the byte located at E5FE is read into

the FLCTRL2 register. It can be written in the ISP or test en-

vironments. It can also be written in the IRE environment

www.national.com

FROMWR

Upon reset of the chip, read security is enabled

and 0000 is returned in all environments except

IRE. The internal program code can only be ex-

ecuted in the IRE environment when read se-

curity is activated.

Upon reset of the chip, write security is enabled

and program and erase operations to the flash

EEPROM program memory in either program-

ming modes are prevented.

Once read/write security is enabled, the odd numbered bytes

from address E5F9 to E5FF cannot be erased. Once a secu-

rity feature has been enabled, it cannot be undone. To pre-

vent the security status from being erased, the ISP and data

memory array cannot be mass erased.

Note:

In flash memory test mode, this condition also pre-

vents the odd numbered bytes of the high endurance flash

EEPROM data memory (F001 to F07F) from being erased;

28