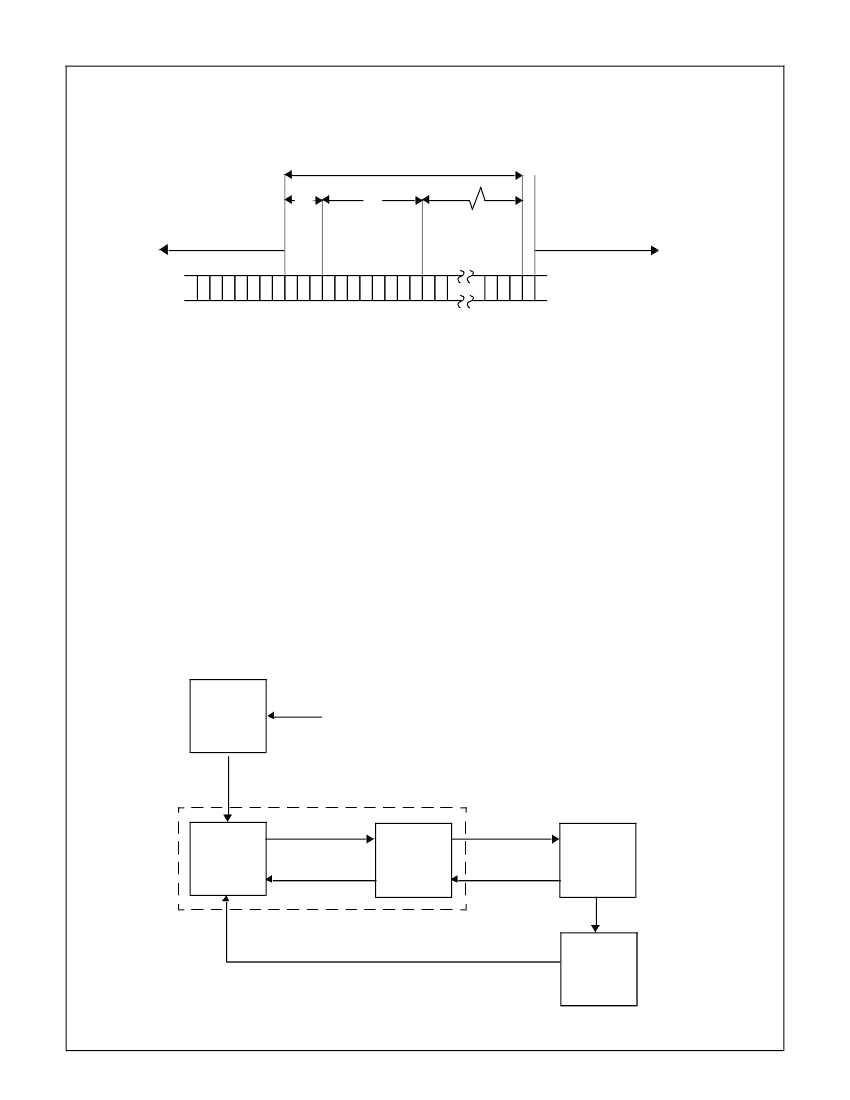

Interframe Space

Data and remote frames are separated from every preceding

frame (data, remote, error and overload frames) by the inter-

frame space (see Figure50). Error and overload frames are

not preceded by an interframe space; they can be transmit-

ted as soon as the condition occurs. The interframe space

consists of a minimum of three bit fields depending on the er-

ror state of the node.

INTERFRAME SPACE

3

INT

ANY FRAME

8

SUSPEND

TRANSMIT

BUS IDLE

START OF FRAME

DATA FRAME OR

REMOTE FRAME

r r r r r r r r r r r r r r r r r r r r

INT = Intermission

Suspend Transmission is only for error passive nodes.

r r r d

Note:

d = dominant

r = recessive

Figure 50.

20.2.2

Error Detection and Management

CAN Interframe Space

鈥?Stuff Error

A stuff error is detected if the bit level after 6 consecu-

tive bit times has not changed in a message field that

has to be coded according to the bit stuffing method.

鈥?Form Error

A form error is detected, if a fixed frame bit (e.g., CRC

delimiter, ACK delimiter) does not have the specified

value. For a receiver, a 鈥榙ominant鈥?bit during the last bit

of End of Frame does not constitute a frame error.

鈥?Bit CRC Error

A CRC error is detected if the remainder of the CRC

calculation of a received CRC polynomial is non-zero.

鈥?Acknowledgment Error

An acknowledgment error is detected whenever a

transmitting node does not get an acknowledgment

from any other node (i.e., when the transmitter does

not receive a 鈥榙ominant鈥?bit during the ACK frame)

There are multiple mechanisms in the CAN protocol to detect

errors and inhibit erroneous modules from disabling all bus

activities. Each CAN module includes two error counters, a

receive and a transmit error counter, for error management.

Error Types

The following errors can be detected:

鈥?Bit Error

A CAN device which is currently transmitting also mon-

itors the bus. If the monitored bit value is different from

the transmitted bit value, a bit error is detected. How-

ever, the reception of a 鈥榙ominant鈥?bit instead of a 鈥榬e-

cessive鈥?bit during the transmission of a passive error

flag, during the stuffed bit stream of the arbitration field

or during the acknowledge slot is not interpreted as a

bit error.

external RESET or

enable CR16CAN

SYNC

11 consecutive 鈥榬ecessive鈥?bits

received

(TEC OR REC) > 95

(TEC OR REC) > 127

ERROR

ACTIVE

(TEC AND REC) < 96

ERROR

WARNING

(TEC AND REC) < 128

ERROR

PASSIVE

TEC > 255

128 occurrences of

11 consecutive 鈥榬ecessive鈥?bits

BUS

OFF

Figure 51. CR16CAN Bus States

www.national.com

92