kHz for Vcc < 2.5V.

鈥?/div>

100 kHz for E temperature range.

FEATURES

鈥?Low power CMOS technology

- Maximum write current 3 mA at 5.5V

- Maximum read current 400

碌

A at 5.5V

- Standby current 100 nA typical at 5.5V

鈥?2-wire serial interface bus, I

2

C compatible

鈥?Cascadable for up to eight devices

鈥?Self-timed ERASE/WRITE cycle

鈥?32-byte page or byte write modes available

鈥?5 ms max write cycle time

鈥?Hardware write protect for entire array

鈥?Output slope control to eliminate ground bounce

鈥?Schmitt trigger inputs for noise suppression

鈥?1,000,000 erase/write cycles guaranteed

鈥?Electrostatic discharge protection > 4000V

鈥?Data retention > 200 years

鈥?8-pin PDIP, SOIC (150 and 208 mil) and TSSOP

packages; 14-pin SOIC package

鈥?Temperature ranges:

- Industrial (I):

-40

掳

C to +85

掳

C

- Automotive (E)

-40

掳

C to +125

掳

C

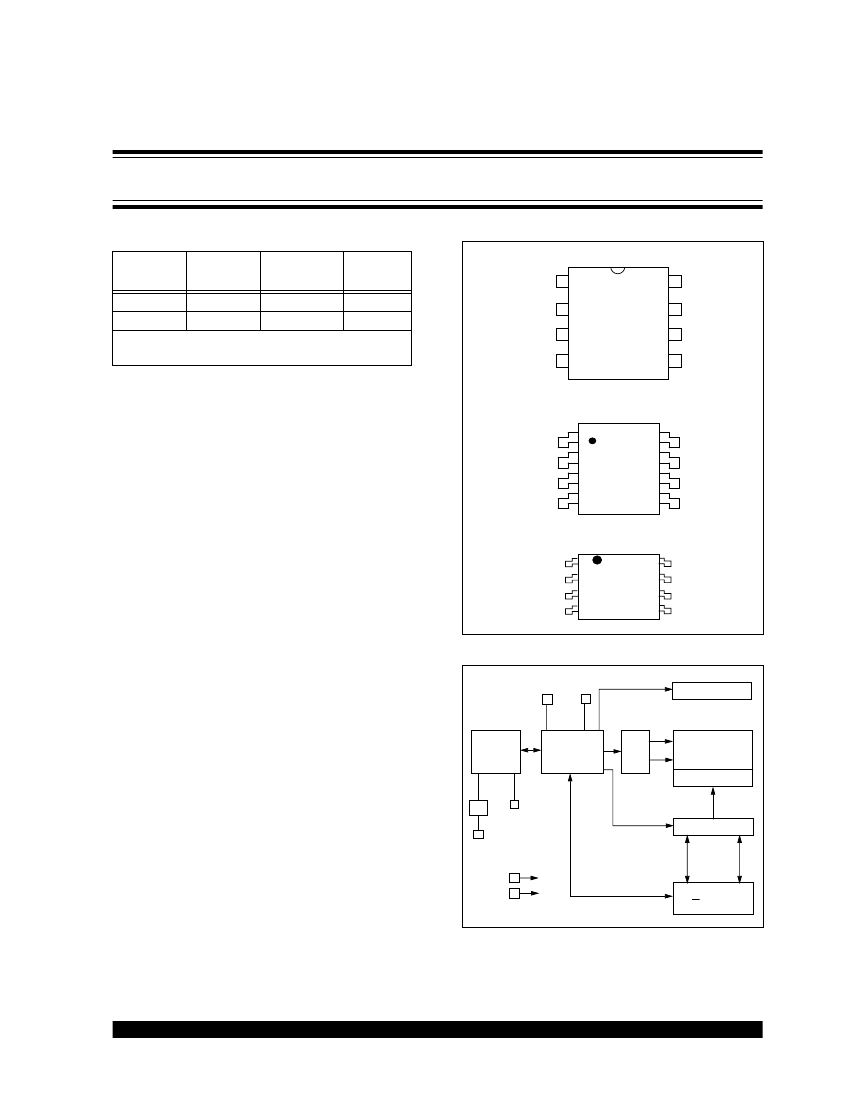

SOIC

A0

A1

A2

V

SS

1

8

V

CC

WP

SCL

SDA

24xx64

2

3

4

7

6

5

TSSOP

WP

Vcc

A0

A1

1

2

3

4

8

7

6

5

SCL

SDA

Vss

A2

24xx64

BLOCK DIAGRAM

A0鈥2

WP

HV GENERATOR

DESCRIPTION

The Microchip Technology Inc. 24AA64/24LC64

(24xx64*) is a 8K x 8 (64K bit) Serial Electrically Eras-

able PROM capable of operation across a broad volt-

age range (1.8V to 5.5V). It has been developed for

advanced, low power applications such as personal

communications or data acquisition. This device also

has a page-write capability of up to 32 bytes of data.

This device is capable of both random and sequential

reads up to the 64K boundary. Functional address lines

allow up to eight devices on the same bus, for up to 512

Kbits address space. This device is available in the

standard 8-pin plastic DIP, 8-pin SOIC (150 and

208 mil), and 8-pin TSSOP.

I/O

CONTROL

LOGIC

MEMORY

CONTROL

LOGIC

XDEC

EEPROM

ARRAY

PAGE LATCHES

I/O

SCL

YDEC

SDA

V

CC

V

SS

SENSE AMP

R/W CONTROL

I

2

C is a trademark of Philips Corporation.

*24xx64 is used in this document as a generic part number for the 24AA64/24LC64 devices.

漏

1998 Microchip Technology Inc.

DS21189B-page 1