鈩?/div>

compatible

鈥?Schmitt trigger, 铿乴tered inputs for noise suppres-

sion

鈥?Output slope control to eliminate ground bounce

鈥?100 kHz (1.8V) and 400 kHz (5V) compatibility

鈥?Self-timed write cycle (including auto-erase)

鈥?Page-write buffer for up to 16 bytes

鈥?2 ms typical write cycle time for page-write

鈥?Hardware write protect for entire memory

鈥?Can be operated as a serial ROM

鈥?ESD protection > 4,000V

鈥?1,000,000 ERASE/WRITE cycles guaranteed

鈥?Data retention > 200 years

鈥?8-pin DIP, 8-lead or 14-lead SOIC packages

鈥?Available for extended temperature ranges

- Commercial (C):

0

掳

C to +70

掳

C

- Industrial (I):

-40

掳

C to +85

掳

C

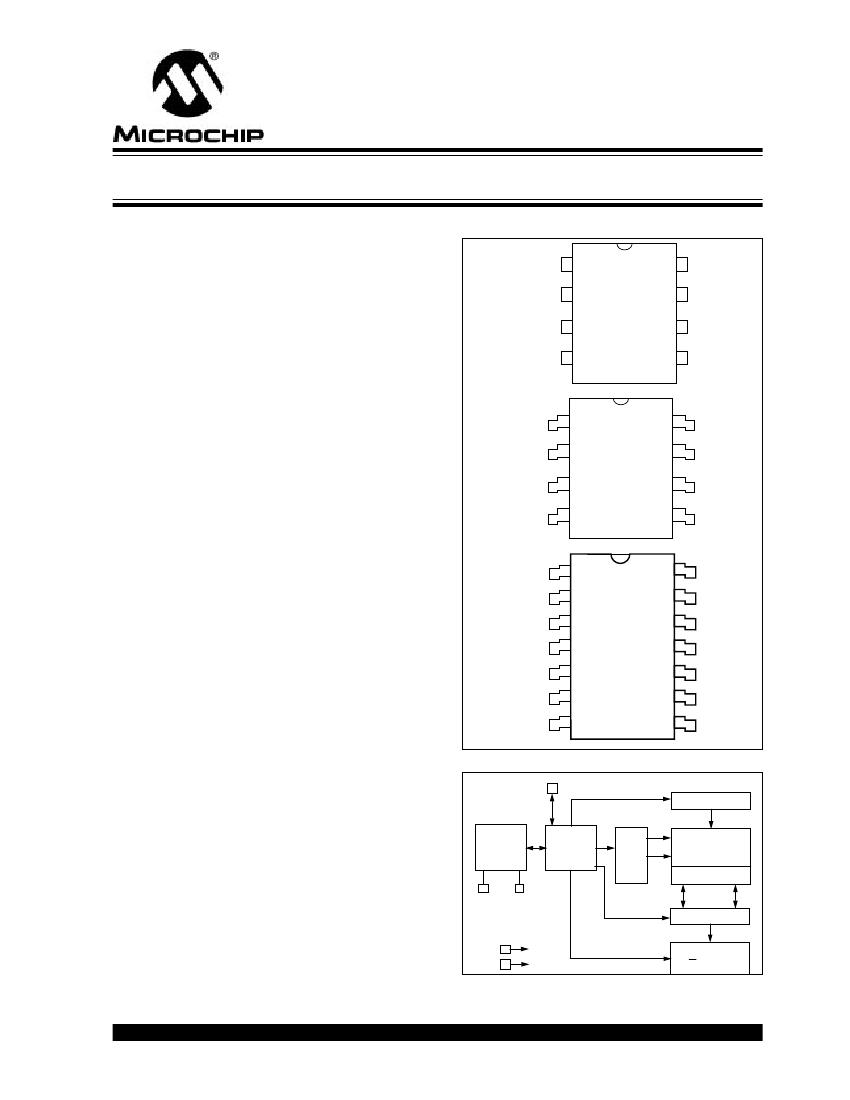

PACKAGE TYPES

DIP

A0

A1

A2

V

SS

1

24AA04/08

2

3

4

8

7

6

5

V

CC

WP

SCL

SDA

8-lead

SOIC

A0

A1

A2

V

SS

1

24AA04/08

8

7

6

5

V

CC

WP

SCL

SDA

2

3

4

14-Lead

SOIC

NC

A0

A1

NC

A2

V

SS

NC

1

2

14

13

NC

V

CC

WP

NC

SCL

SDA

NC

24AA04/08

3

4

5

6

7

12

11

10

9

8

DESCRIPTION

The Microchip Technology Inc. 24AA04/08 is a 4K bit or

8K bit Electrically Erasable PROM. The device is orga-

nized as two or four blocks of 256 x 8-bit memory with

a two wire serial interface. Low voltage design permits

operation down to 1.8 volts with standby and active cur-

rents of only 3

碌

A and 1 mA respectively. The 24AA04/

08 also has a page-write capability for up to 16 bytes of

data. The 24AA04/08 is available in the standard 8-pin

DIP and both 8-lead and 14-lead surface mount SOIC

packages.

BLOCK DIAGRAM

WP

HV GENERATOR

I/O

CONTROL

LOGIC

MEMORY

CONTROL

LOGIC

XDEC

EEPROM

ARRAY

PAGE LATCHES

SDA

SCL

YDEC

V

CC

V

SS

SENSE AMP

R/W CONTROL

I

2

C is a trademark of Philips Corporation.

漏

1996 Microchip Technology Inc.

DS21053E-page 1

This document was created with FrameMaker 4 0 4