Philips Semiconductors

Product specification

TrenchMOS餂?transistor

Logic level FET

GENERAL DESCRIPTION

N-channel enhancement mode logic

level field-effect power transistor in a

plastic envelope available in

TO220AB and SOT404 . Using

鈥檛rench鈥?technology which features

very low on-state resistance. It is

intended for use in automotive and

general

purpose

switching

applications.

BUK9515-100A

BUK9615-100A

QUICK REFERENCE DATA

SYMBOL

V

DS

I

D

P

tot

T

j

R

DS(ON)

PARAMETER

Drain-source voltage

Drain current (DC)

Total power dissipation

Junction temperature

Drain-source on-state

resistance

V

GS

= 5 V

V

GS

= 10 V

MAX.

100

75

230

175

15

14.4

UNIT

V

A

W

藲C

m鈩?/div>

m鈩?/div>

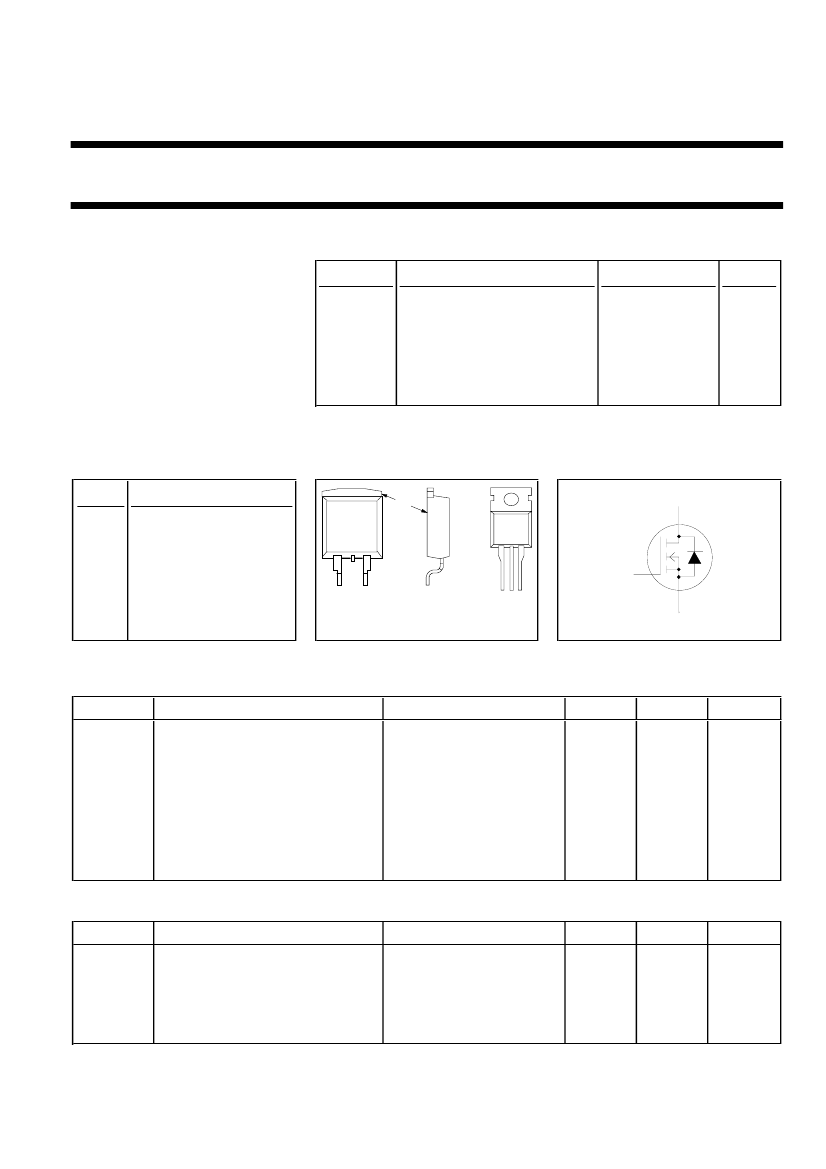

PINNING

TO220AB & SOT404

PIN

1

2

3

DESCRIPTION

gate

drain

2

PIN CONFIGURATION

mb

tab

SYMBOL

d

g

3

SOT404

1 2 3

source

1

tab/mb drain

TO220AB

s

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL

V

DS

V

DGR

卤V

GS

卤V

GSM

I

D

I

D

I

DM

P

tot

T

stg

, T

j

PARAMETER

Drain-source voltage

Drain-gate voltage

Gate-source voltage

Non-repetitive gate-source voltage

Drain current (DC)

Drain current (DC)

Drain current (pulse peak value)

Total power dissipation

Storage & operating temperature

CONDITIONS

-

R

GS

= 20 k鈩?/div>

-

t

p

鈮?0碌S

T

mb

= 25 藲C

T

mb

= 100 藲C

T

mb

= 25 藲C

T

mb

= 25 藲C

-

MIN.

-

-

-

-

-

-

-

-

- 55

MAX.

100

100

10

15

75

53

313

230

175

UNIT

V

V

V

V

A

A

A

W

藲C

THERMAL RESISTANCES

SYMBOL

R

th j-mb

R

th j-a

R

th j-a

PARAMETER

Thermal resistance junction to

mounting base

Thermal resistance junction to

ambient(TO220AB)

Thermal resistance junction to

ambient(SOT404)

CONDITIONS

-

in free air

Minimum footprint, FR4

board

TYP.

-

60

50

MAX.

0.65

-

-

UNIT

K/W

K/W

K/W

November 1999

1

Rev 1.000