鈥?/div>

4-multiplier configuration

Single phase-locked loop architecture

Phase Alignment

Low jitter, high accuracy outputs

Output enable pin

3.3V operation

5V Tolerant input

Internal loop filter

8-pin 150-mil SOIC package

Commercial and Industrial Temperature available

Benefits

鈥?1/2x, 1x, 1x, 2x Ref

鈥?10 MHz to 166.67 MHz operating range (reference input

from 20 MHz to 83.33 MHz)

鈥?All outputs will have a consistent phase relationship

with each other and the reference input

鈥?Meets critical timing requirements

鈥?Enables design flexibility and lower power

consumption

鈥?Supports industry standard design platforms

鈥?Allows flexibility on Reference input

鈥?Alleviates the need for external components

鈥?Industry standard packaging saves on board space

鈥?Suitable for wide spectrum of applications

Selector Guide

Part Number

CY2300SC

CY2300SI

Outputs

4

4

Input Frequency Range

20 MHz鈥?3.33 MHz

20 MHz鈥?3.33 MHz

Output Frequency Range

10 MHz鈥?66.67 MHz

10 MHz鈥?66.6 7MHz

Specifics

Commercial Temperature

Industrial Temperature

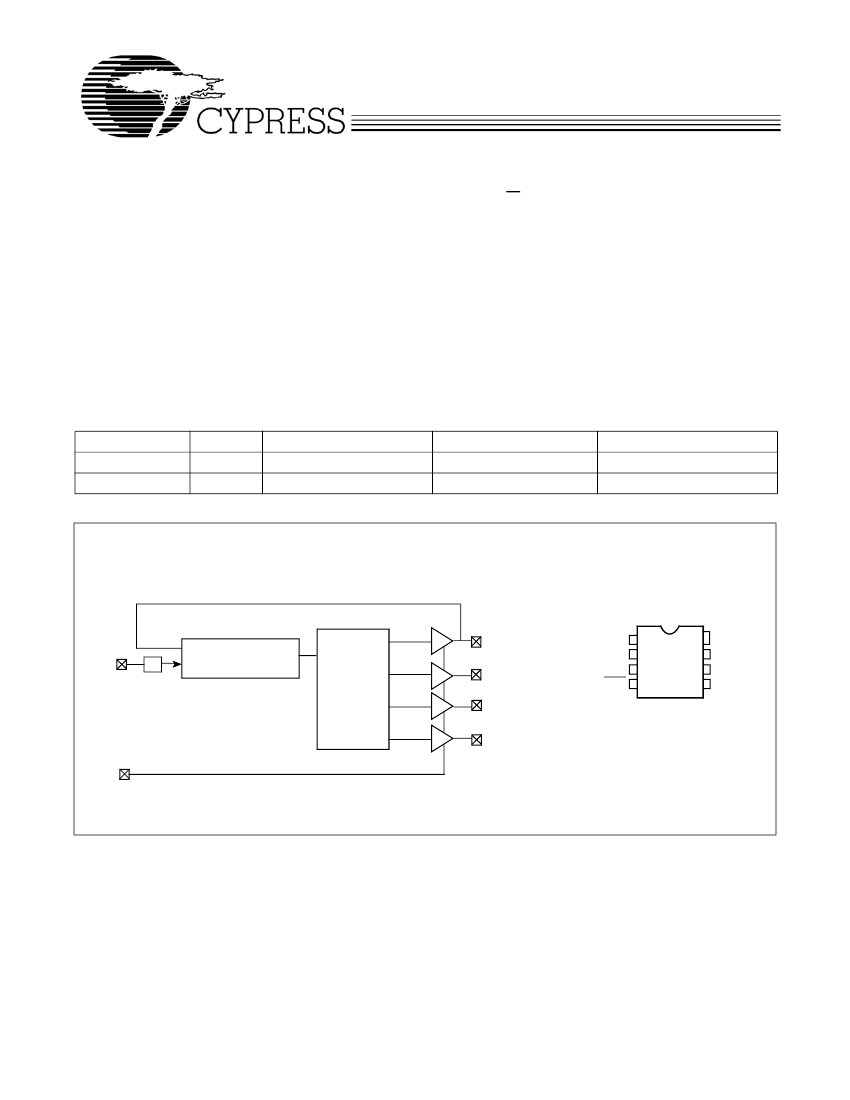

Block Diagram

FBK

Pin Configuration

8-pin SOIC

Top View

1/2xREF

REFIN

/2

PLL

Divider

Logic

REF

REF

1/2xREF

GND

REFIN

REF

1

2

3

4

8

7

6

5

OE

V

DD

2xREF

REF

2xREF

OE

Cypress Semiconductor Corporation

Document #: 38-07252 Rev. *B

鈥?/div>

3901 North First Street

鈥?/div>

San Jose

鈥?/div>

CA 95134 鈥?408-943-2600

Revised July 26, 2004