鈮?/div>

1碌A (max.)

CMOS power levels

True TTL input and output compatibility:

鈥?V

OH

= 3.3V (typ.)

鈥?V

OL

= 0.3V (typ.)

High Drive outputs (-15mA I

OH

, 48mA I

OL

)

Meets or exceeds JEDEC standard 18 specifications

Military product compliant to MIL-STD-883, Class B and DESC

listed (dual marked)

Power off disable outputs permit "live insertion"

Available in the following packages:

鈥?Industrial: SOIC, SSOP, QSOP, TSSOP

鈥?Military: CERDIP, LCC

DESCRIPTION:

The FCT573Tis an octal transparent latch built using an advanced dual

metal CMOS technology. These octal latches have 3-state outputs and are

intended for bus oriented applications. The flip-flops appear transparent to

the data when Latch Enable (LE) is high. When LE is low, the data that meets

the set-up time is latched. Data appears on the bus when the Output Enable

(OE) is low. When

OE

is high, the bus output is in the high-impedance state.

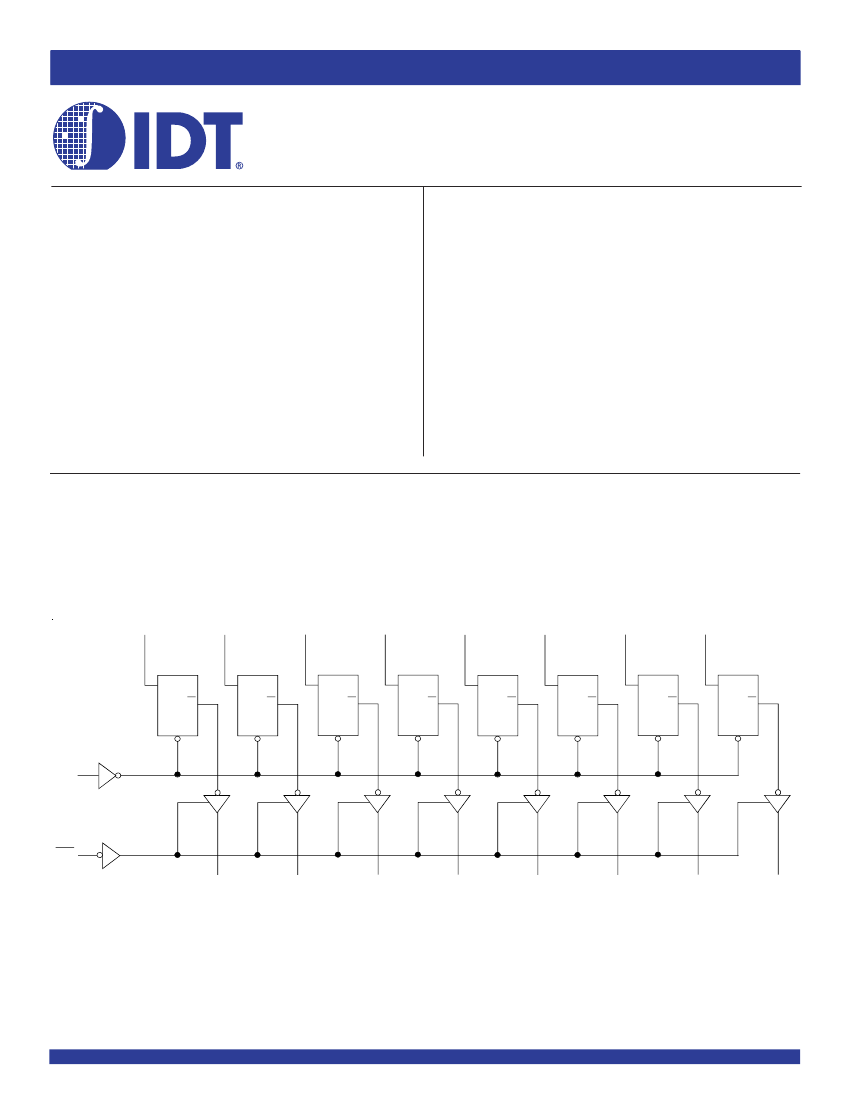

FUNCTIONAL BLOCK DIAGRAM

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

O

G

D

O

G

D

O

G

D

O

G

D

O

G

D

O

G

D

O

G

D

O

G

LE

OE

O

0

O

1

O

2

O

3

O

4

O

5

O

6

O

7

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

1

JUNE 2002

DSC-5948/3

漏 2002 Integrated Device Technology, Inc.