CMOS PARALLEL-TO-SERIAL FIFO

2048

X

9

4096

X

9

Integrated Device Technology, Inc.

IDT72131

IDT72141

FEATURES:

鈥?35ns parallel port access time, 45ns cycle time

鈥?50MHz serial port shift rate

鈥?Expandable in depth and width with no external

components

鈥?Programmable word lengths including 7-9, 16-18, 32-36

bit using Flexishift鈩?serial output without using any

additional components

鈥?Multiple status flags: Full, Almost-Full (1/8 from full),

Half-Full, Almost Empty (1/8 from empty), and Empty

鈥?Asynchronous and simultaneous read and write

operations

鈥?Dual-Port zero fall-through architecture

鈥?Retransmit capability in single device mode

鈥?Produced with high-performance, low power CMOS

technology

鈥?Available in 28-pin plastic DIP

鈥?Industrial temperature range (-40

o

C to +85

o

C) is avail-

able, tested to military electrical specifications

DESCRIPTION:

The IDT72131/72141 are high-speed, low power parallel-

to-serial FIFOs. These FIFOs are ideally suited to serial

communications applications, tape/disk controllers, and local

area networks (LANs). The IDT72131/72141 can be config-

ured with the IDTs serial-to-parallel FIFOs (IDT72132/72142)

for bidirectional serial data buffering.

The FIFO has a 9-bit parallel input port and a serial output

port. Wider and deeper parallel-to-serial data buffers can be

built using multiple IDT72131/72141 chips. IDTs unique

Flexishift serial expansion logic (SOX,

NR

) makes width

expansion possible with no additional components. These

FIFOs will expand to a variety of word widths including 8, 9, 16,

and 32 bits. The IDT72131/141 can also be directly connected

for depth expansion.

Five flags are provided to monitor the FIFO. The full and

empty flags prevent any FIFO data overflow or underflow

conditions. The almost-full (7/8), half-full, and almost empty

(1/8) flags signal memory utilization within the FIFO.

The IDT72131/72141 is fabricated using IDTs high-speed

submicron CMOS technology.

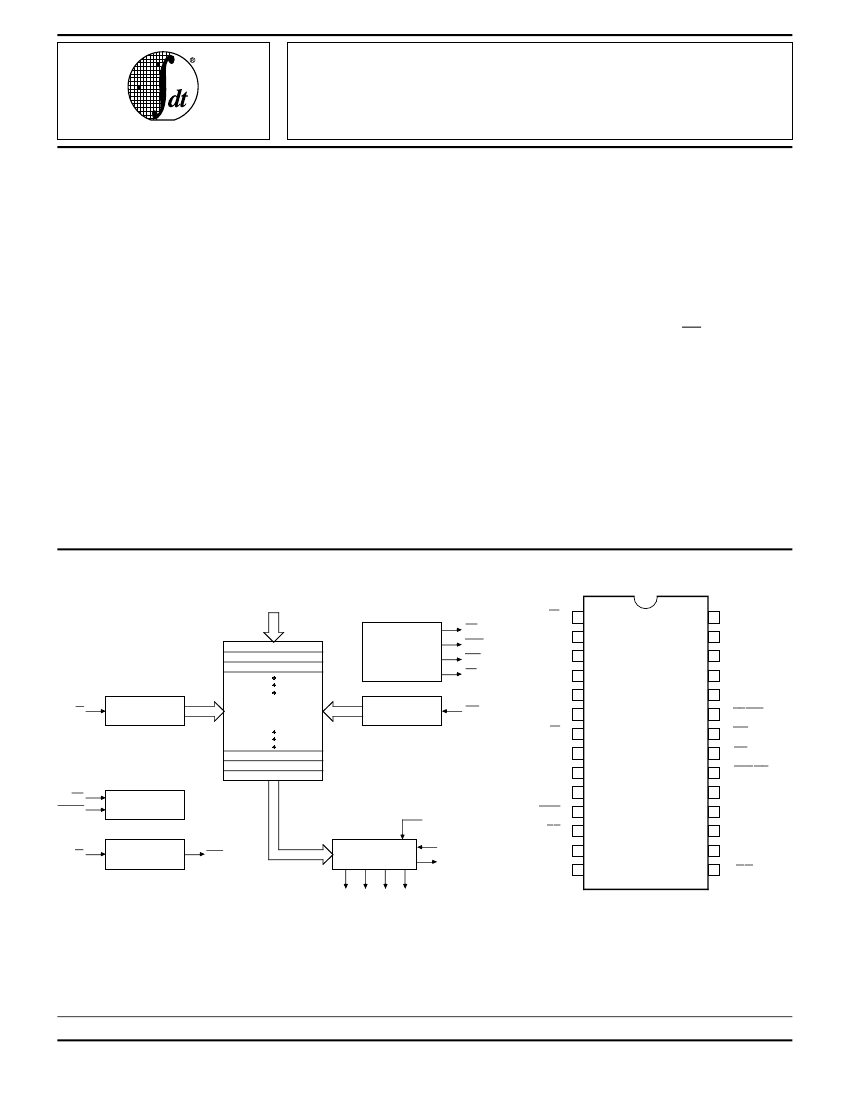

FUNCTIONAL BLOCK DIAGRAM

D

0

-D

8

PIN CONFIGURATION

W

D

4

D

3

D

2

D

1

NEXT READ

POINTER

NR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

Vcc

D

5

D

6

D

7

D

8

EF

FLAG

LOGIC

AEF

/HF

FF

WRITE

POINTER

RAM ARRAY

2048 x 9

4096 x 9

W

D

0

XI

SOX

SOCP

SO

P28-1

&

C28-3

23

22

21

20

19

18

17

16

15

FL/RT

RS

EF

XO/HF

GND

Q

8

Q

7

Q

6

RS

FL/RT

RESET LOGIC

SOCP

EXPANSION

LOGIC

SERIAL OUTPUT

CIRCUITRY

SOX

SO

AEF

FF

Q

4

GND

XI

XO/

NR

Q

4

Q

6

Q

7

Q

8

2751 drw 01

DIP

TOP VIEW

2751 drw 02a

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGES

漏1996

Integrated Device Technology, Inc.

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

DECEMBER 1996

DSC-2751/6

5.34

1